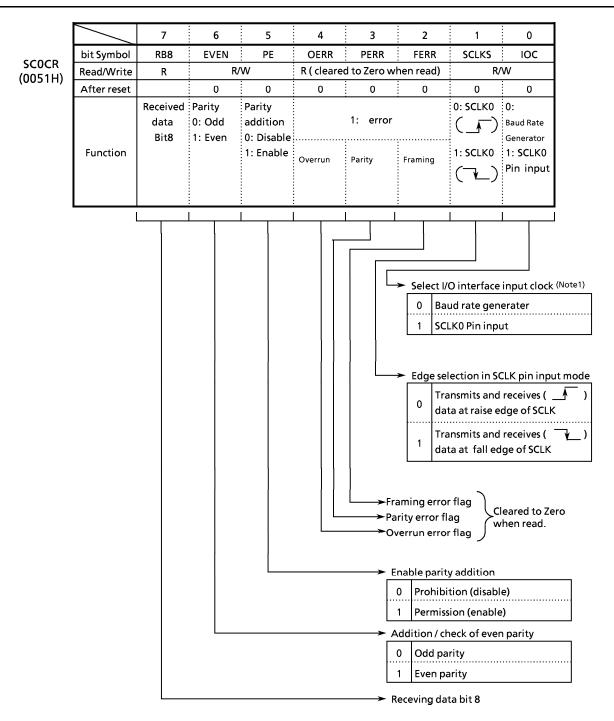

## **TOSHIBA**

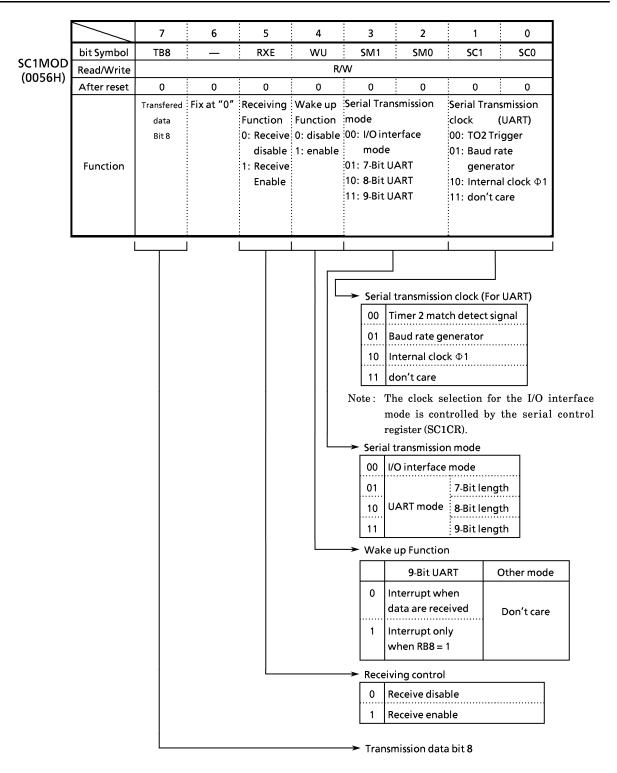

TOSHIBA Original CMOS 16-Bit Microcontroller

TLCS-900/H Series

TMP95C061BFG TMP95C061BDFG

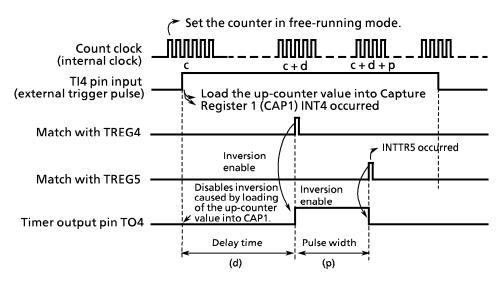

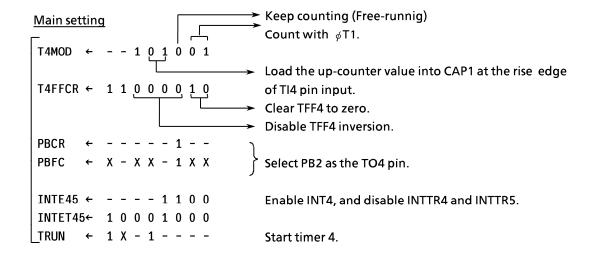

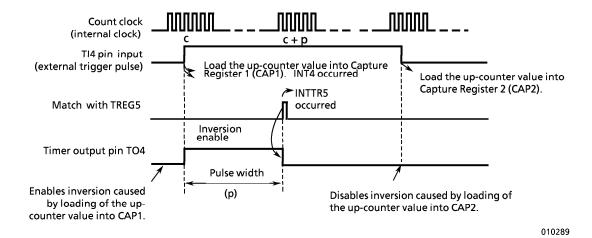

## **TOSHIBA CORPORATION**

Semiconductor Company

# **Preface**

Thank you very much for making use of Toshiba microcomputer LSIs. Before use this LSI, refer the section, "Points of Note and Restrictions". Especially, take care below cautions.

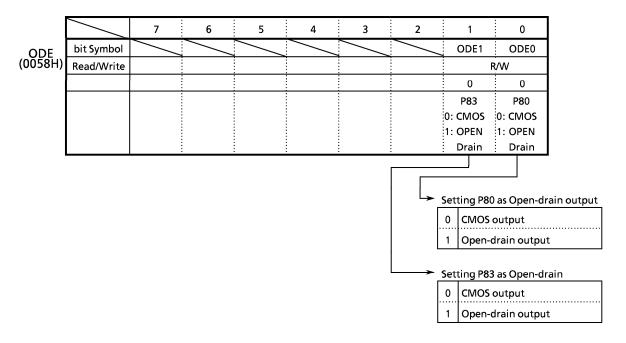

## \*\*CAUTION\*\*

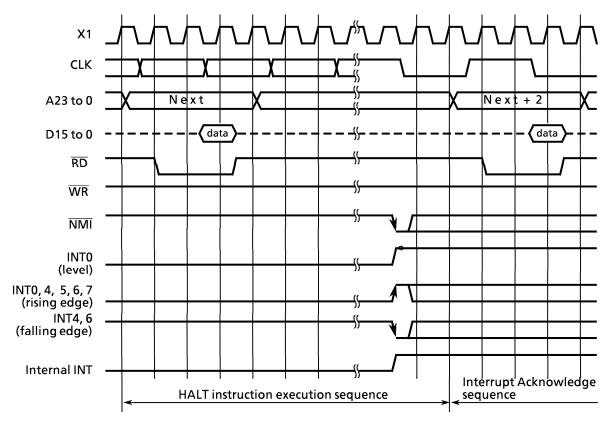

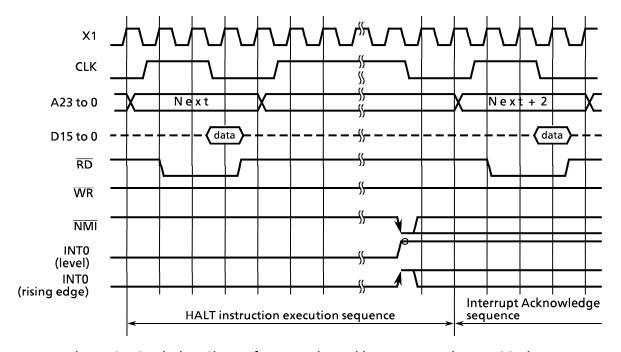

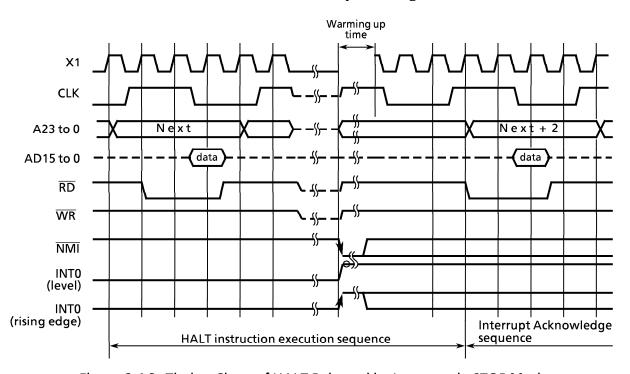

How to release the HALT mode

Usually, interrupts can release all halts status. However, the interrupts =  $(\overline{NMI}, INTO)$ , which can release the HALT mode may not be able to do so if they are input during the period CPU is shifting to the HALT mode (for about 3 clocks of X1) with IDLE or STOP mode. (In this case, an interrupt request is kept on hold internally.)

If another interrupt is generated after it has shifted to HALT mode completely, halt status can be released without difficultly. The priority of this interrupt is compare with that of the interrupt kept on hold internally, and the interrupt with higher priority is handled first followed by the other interrupt.

# **Document Change Notification**

The purpose of this notification is to inform customers about the launch of the Pb-free version of the device. The introduction of a Pb-free replacement affects the datasheet. Please understand that this notification is intended as a substitute for a revision of the datasheet.

Changes to the datasheet may include the following, though not all of them may apply to this particular device.

#### 1. Part number

Example: TMPxxxxxxFG TMPxxxxxxFG

All references to the previous part number were left unchanged in body text. The new part number is indicated on the prelims pages (cover page and this notification).

#### 2. Package code and package dimensions

Example: LQFP100-P-1414-0.50C LQFP100-P-1414-0.50F

All references to the previous package code and package dimensions were left unchanged in body text. The new ones are indicated on the prelims pages.

#### 3. Addition of notes on lead solderability

Now that the device is Pb-free, notes on lead solderability have been added.

Ι

#### 4. RESTRICTIONS ON PRODUCT USE

The previous (obsolete) provision might be left unchanged on page 1 of body text. A new replacement is included on the next page.

#### 5. Publication date of the datasheet

The publication date at the lower right corner of the prelims pages applies to the new device.

#### 1. Part number

## 2. Package code and dimensions

| Previous Part Number (in Body Text) | Previous Package Code (in Body Text) | New Part Number | New Package Code     |  |

|-------------------------------------|--------------------------------------|-----------------|----------------------|--|

| TMP95C061BF                         | P-QFP100-1414-0.50                   | TMP95C061BFG    | QFP100-P-1414-0.50   |  |

| _ (Note)                            | _ (Note)                             | TMP95C061BDFG   | LQFP100-P-1414-0.50F |  |

Note: Pb-containing variant not available.

## 3. Addition of notes on lead solderability

The following solderability test is conducted on the new device.

#### Solderability

| Test Parameter | Test Condition                                                                                                                                                                                                                                                               | Note                                               |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Solderability  | Use of Sn-37Pb solder Bath Solder bath temperature = 230°C, Dipping time = 5 seconds The number of times = one, Use of R-type flux Use of Sn-3.0Ag-0.5Cu solder bath Solder bath temperature = 245°C, Dipping time = 5 seconds The number of times = one, Use of R-type flux | Pass:<br>Solderability rate until forming<br>≥ 95% |

## 4. RESTRICTIONS ON PRODUCT USE

It replaces the "RESTRICTIONS ON PRODUCT USE" on page 1 of body text. For details, see the attached RESTRICTIONS ON PRODUCT USE.

#### 5. Publication date of the datasheet

The publication date of this datasheet is printed at the lower right corner of this notification.

<sup>\*:</sup> For the dimensions of the new package, see the attached Package Dimensions diagram.

(Annex)

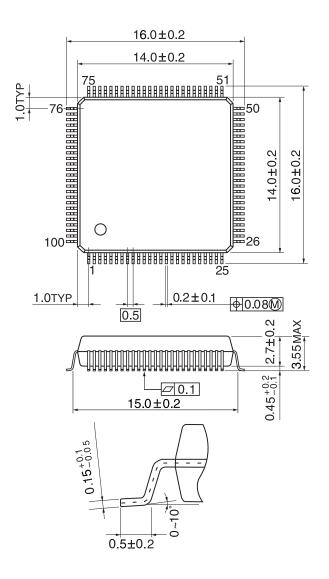

# Package Dimensions

QFP100-P-1414-0.50

$Unit: \, mm$

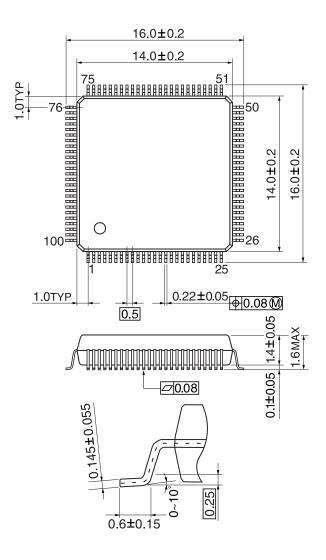

## LQFP100-P-1414-0.50F

Unit: mm

#### RESTRICTIONS ON PRODUCT USE

- Toshiba Corporation, and its subsidiaries and affiliates (collectively "TOSHIBA"), reserve the right to make changes to the information in this document, and related hardware, software and systems (collectively "Product") without notice.

- This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

- Product is intended for use in general electronics applications (e.g., computers, personal equipment, office equipment, measuring equipment, industrial robots and home electronics appliances) or for specific applications as expressly stated in this document. Product is neither intended nor warranted for use in equipment or systems that require extraordinarily high levels of quality and/or reliability and/or a malfunction or failure of which may cause loss of human life, bodily injury, serious property damage or serious public impact ("Unintended Use"). Unintended Use includes, without limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, devices related to electric power, and equipment used in finance-related fields. Do not use Product for Unintended Use unless specifically permitted in this document.

- Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

- ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE

FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY

WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR

LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND

LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO

SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS

FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). Product and related software and technology may be controlled under the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and regulations.

- Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product.

Please use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. TOSHIBA assumes no liability for damages or losses occurring as a result of noncompliance with applicable laws and regulations.

V

# CMOS 16-bit Microcontroller TMP95C061BF

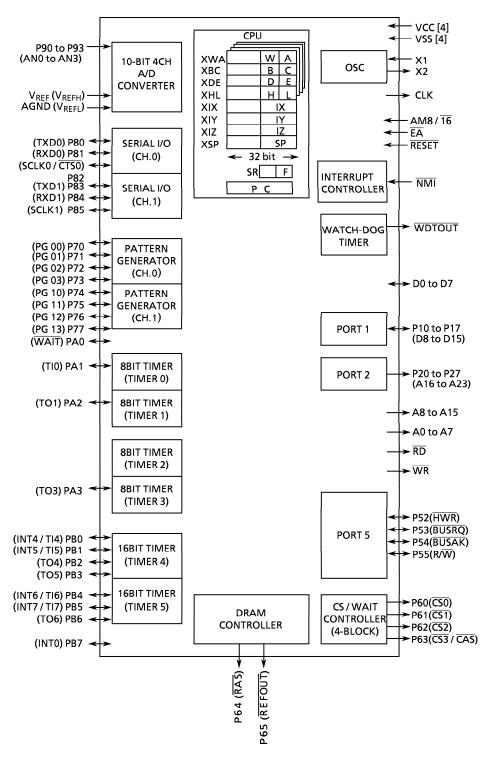

#### 1. Outline and Device Characteristics

TMP95C061BF is high-speed advanced 16-bit microcontroller developed for controlling medium to large-scale equipment. TMP95C061BF is housed in an 100-pin mini flat package (QFP100-P-1414-0.50). TMP95C061BEF is housed in QFP100-P-2222-0.80A package.

Device characteristics are as follows:

Original High speed 16-bit CPU (900/H CPU)

- TLCS-90/900 instruction mnemonic upward compatible.

- 16M-byte linear address space

- General-purpose registers and register bank system

- 16-bit multiplication / division and bit transfer / arithmetic instructions

- Micro DMA : 4 channels (640 ns / 2 bytes at 25 MHz)

- Minimum instruction execution time: 160 ns at 25 MHz (2)

- : None Internal RAM Internal ROM : None

- **(4)** External memory expansion

- Can be expanded up to 16 Mbytes (for both programs and data).

- AM8 /  $\overline{16}$  pin (select the external data bus width)

- Can mix 8- and 16-bit external data buses. ... Dynamic data bus sizing

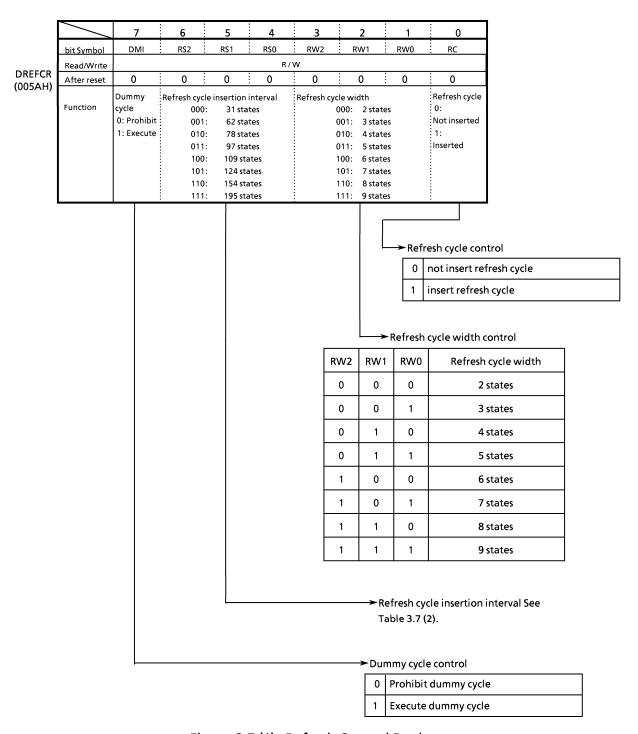

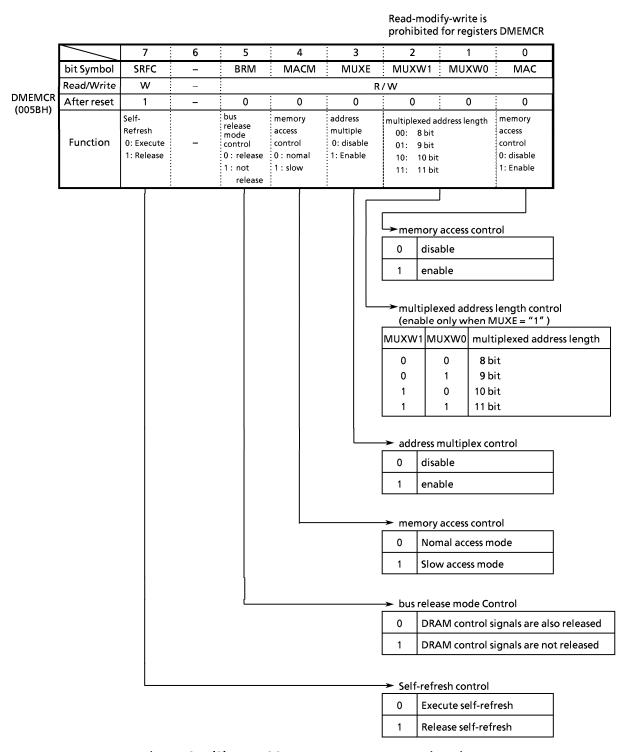

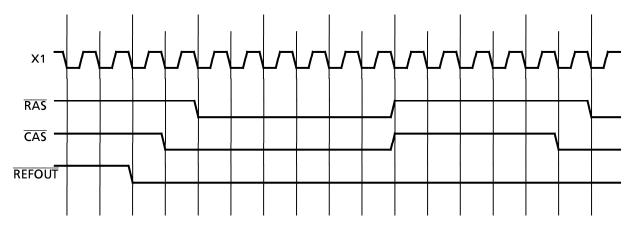

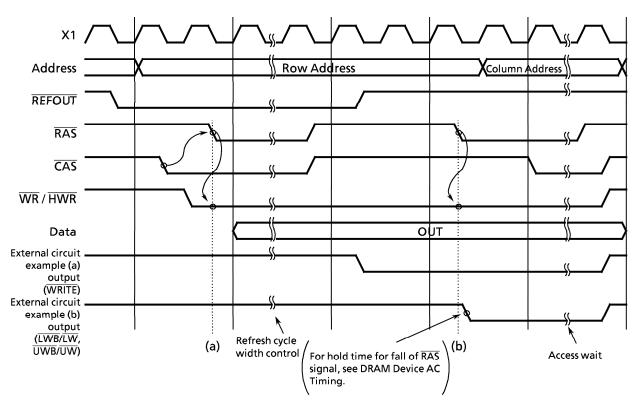

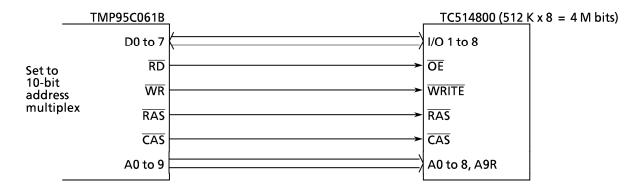

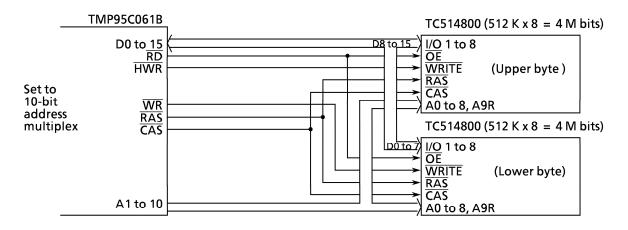

- DRAM Controller (5)

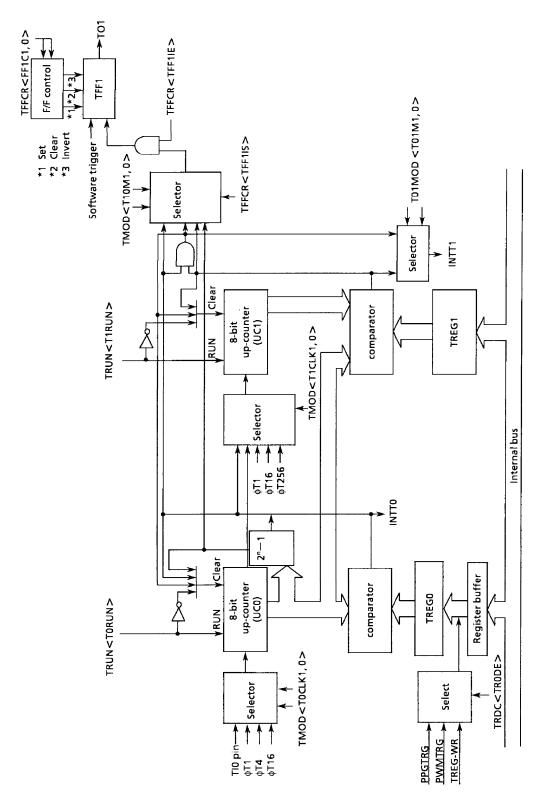

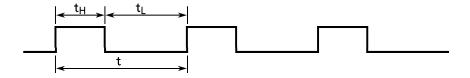

**(6)** 8-bit timer : 4 channels 16-bit timer : 2 channels (7)

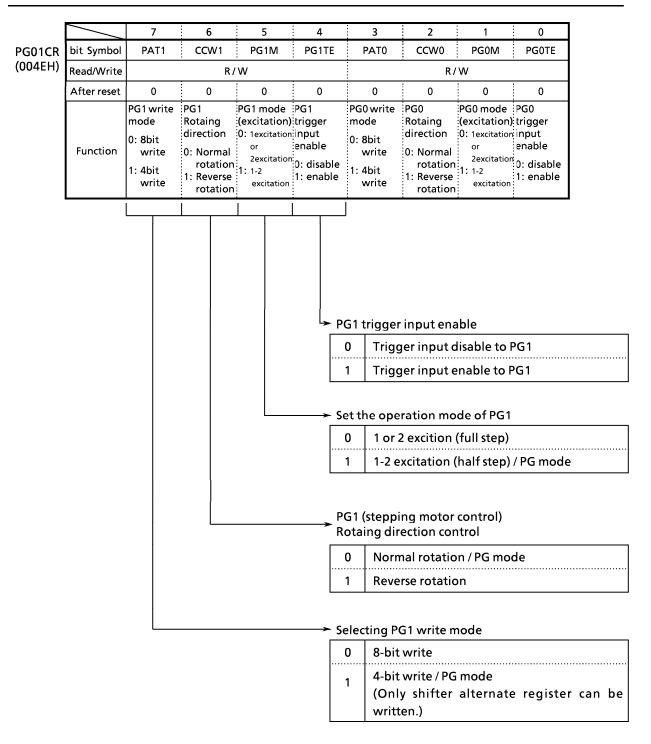

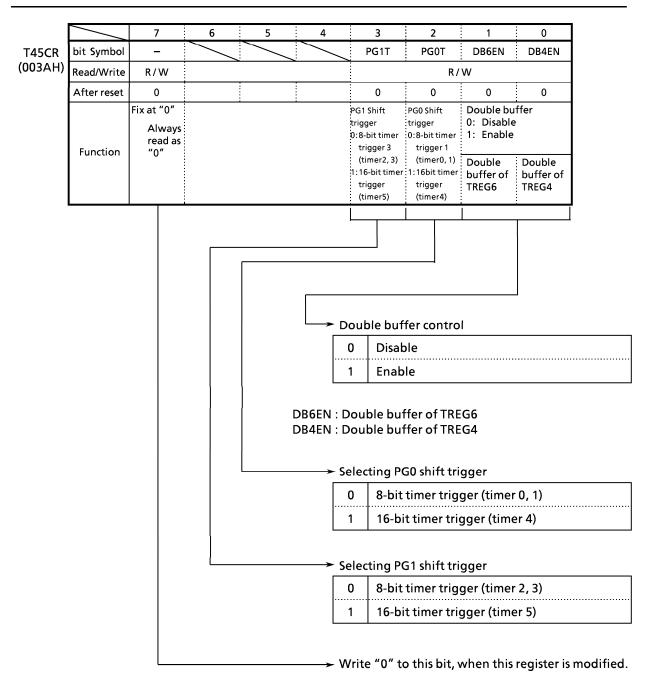

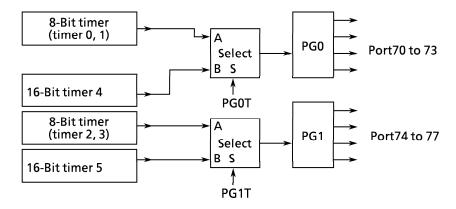

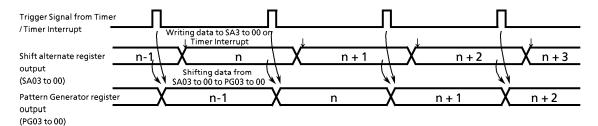

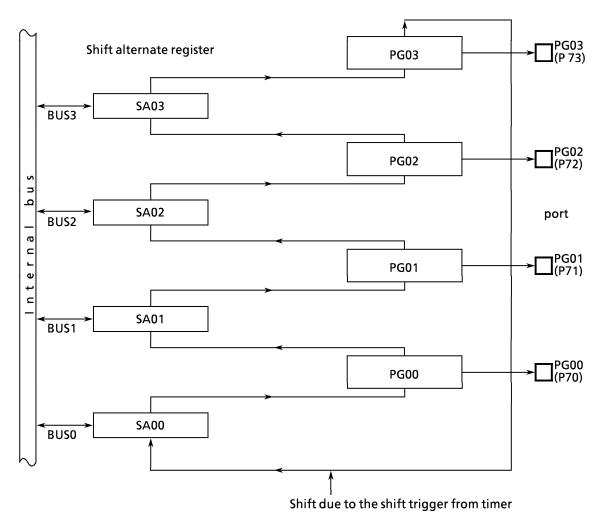

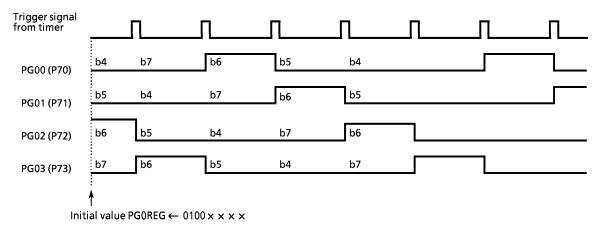

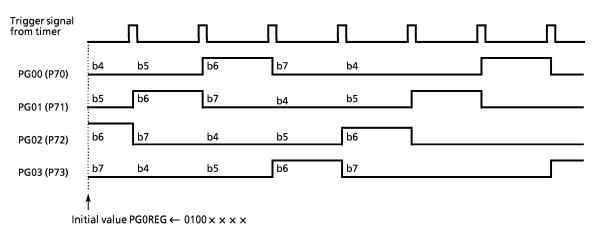

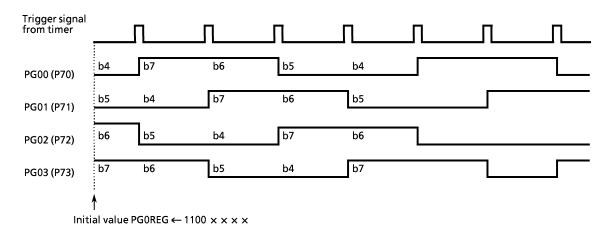

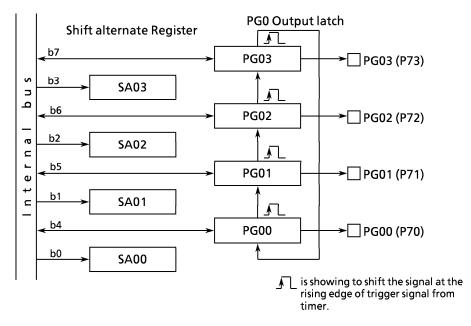

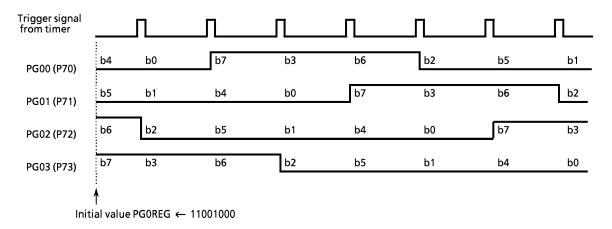

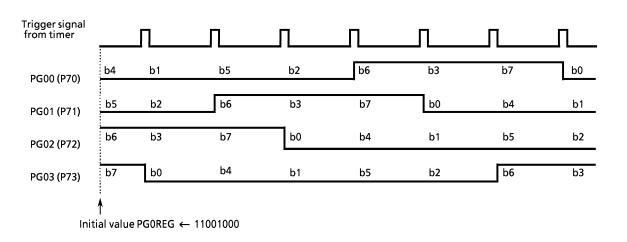

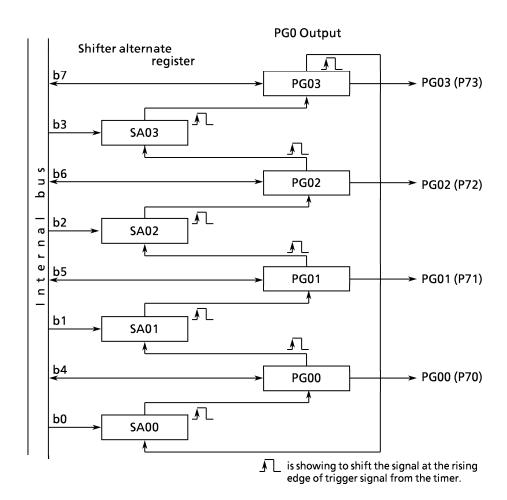

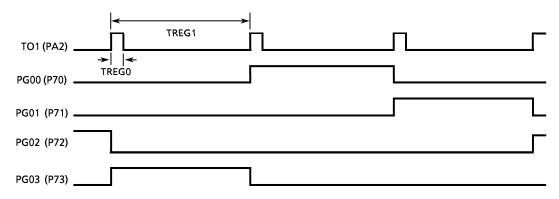

(8) Pattern generator : 4 bits, 2 channels

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance / Handling Precautions.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA

- making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

95C061B-1 2003-03-31

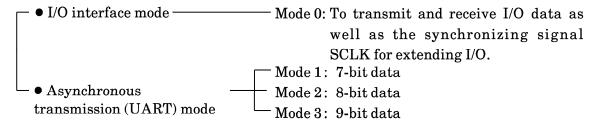

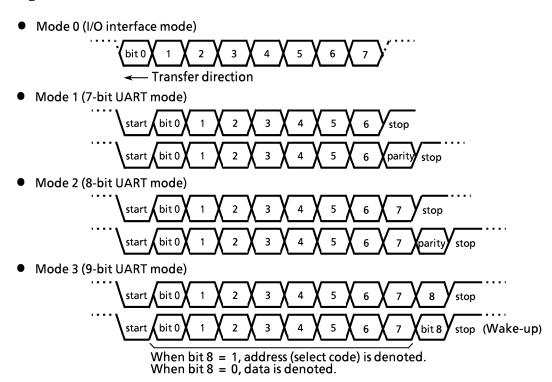

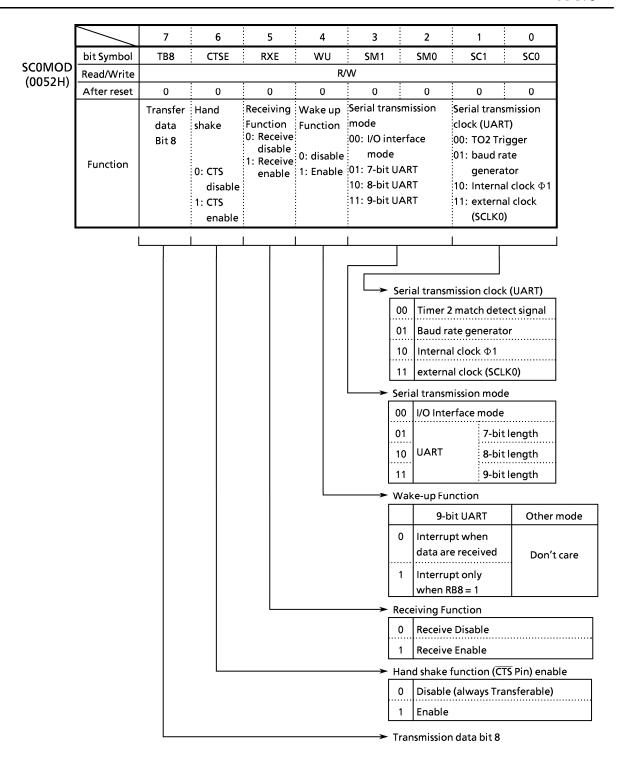

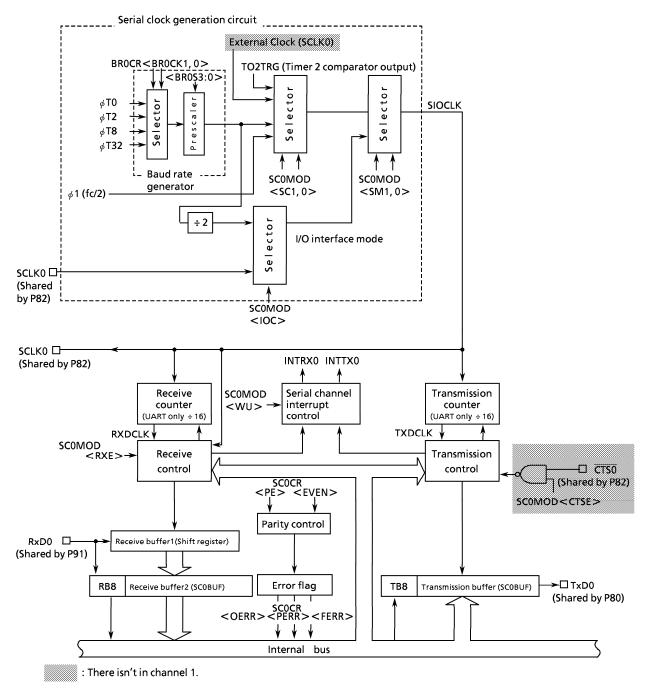

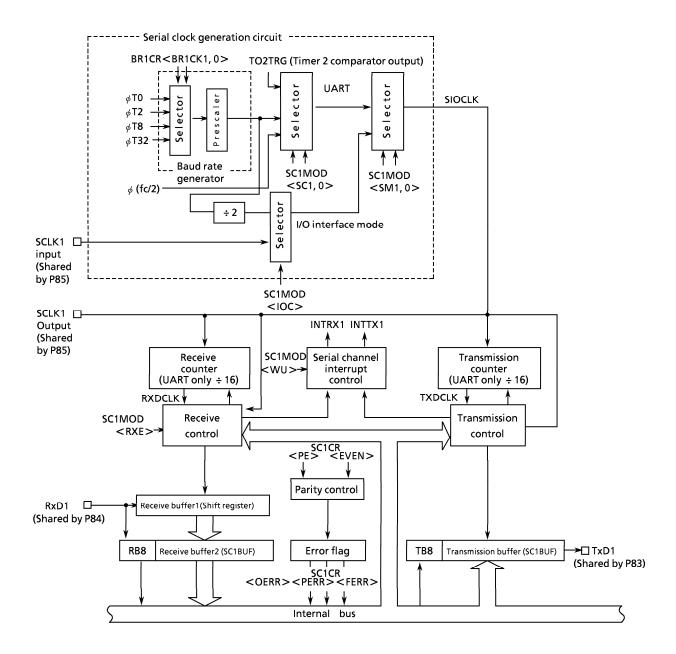

(9) Serial interface :2 channels

(Only for channel 0, external clock can be used in UART mode.)

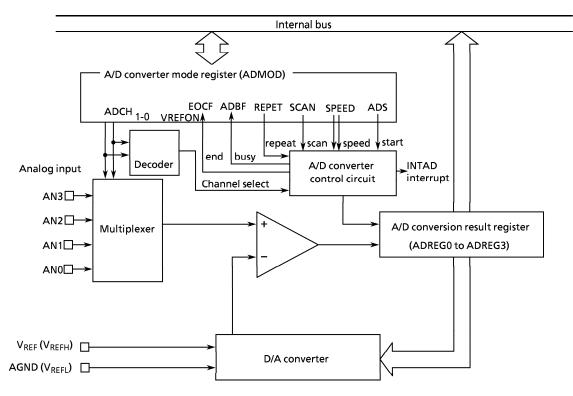

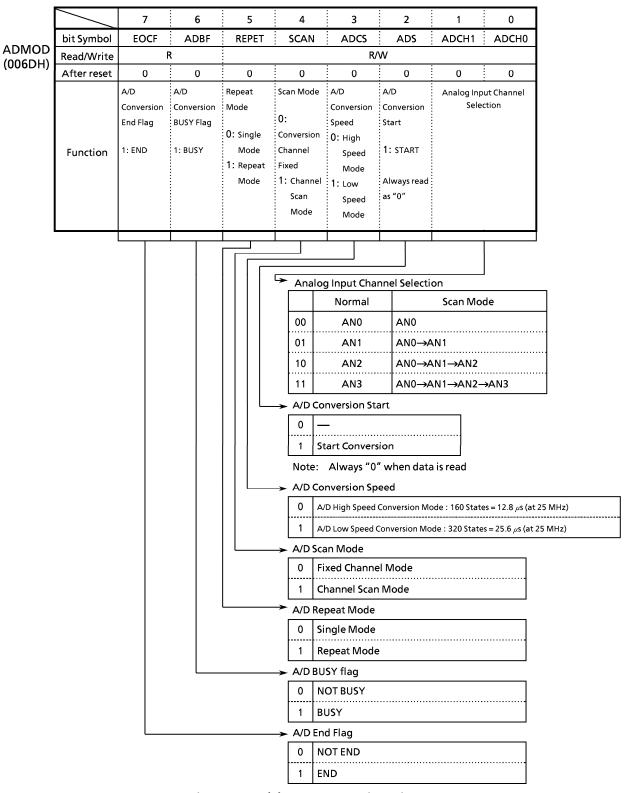

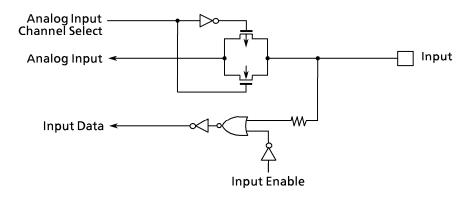

(10) 10-bit A/D converter :4 channels

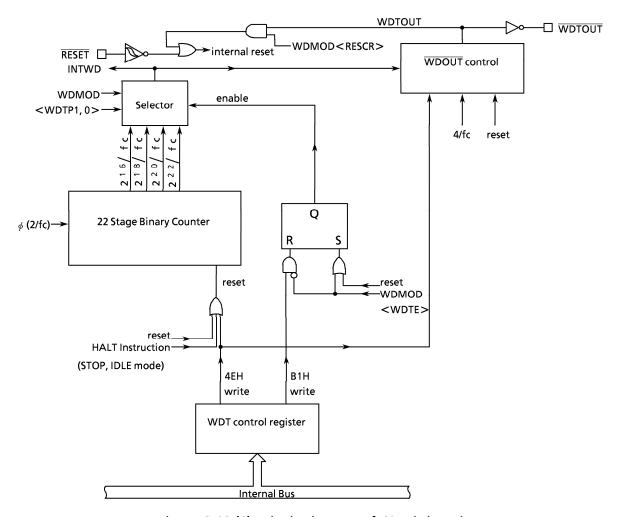

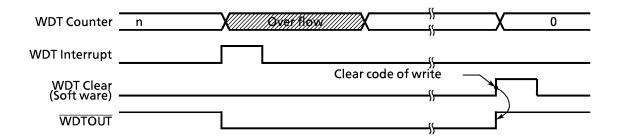

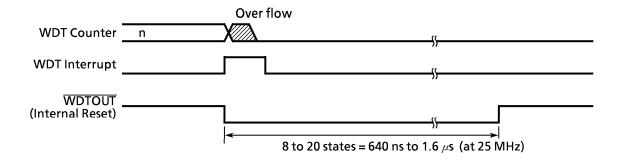

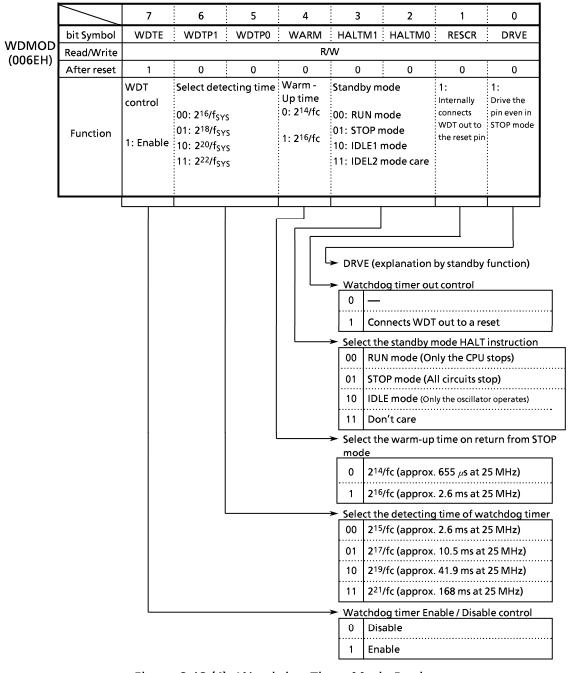

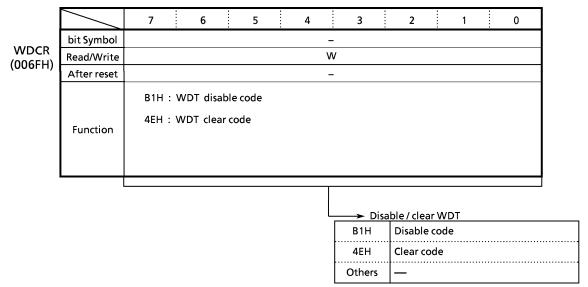

(11) Watchdog timer

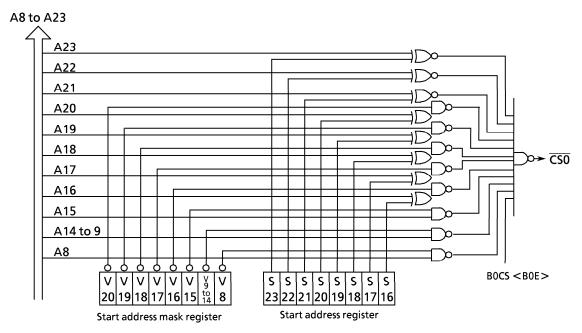

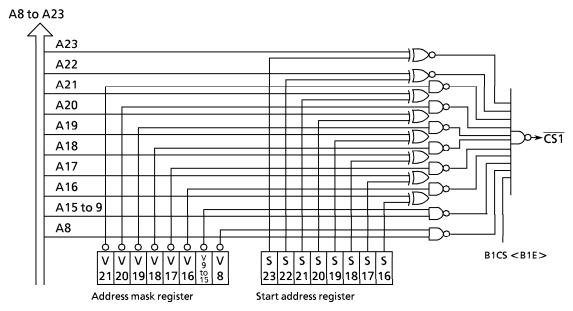

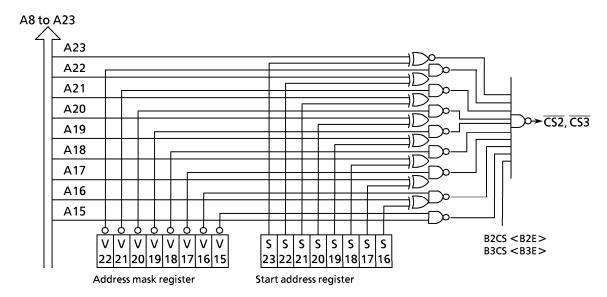

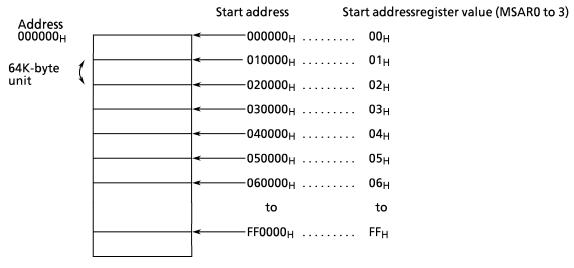

(12) Chip select / wait controller :4 blocks

(13) Interrupt functions

• 2 CPU interrupts ...... SWI instruction, and Illegal instruction

18 internal interrupts ... 7-level priority can be set.

6 external interrupts .... 7-level priority can be set.

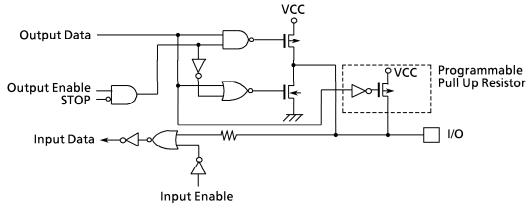

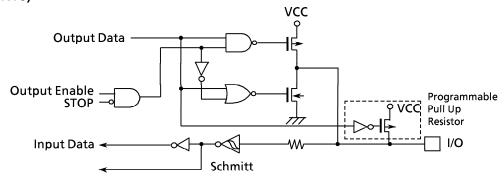

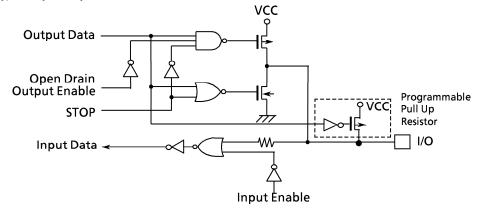

(14) I/O ports 56 pins

(15) Standby function :3 HALT modes (RUN, IDLE, STOP)

95C061B-2 2003-03-31

Figure 1 TMP95C061B Block Diagram

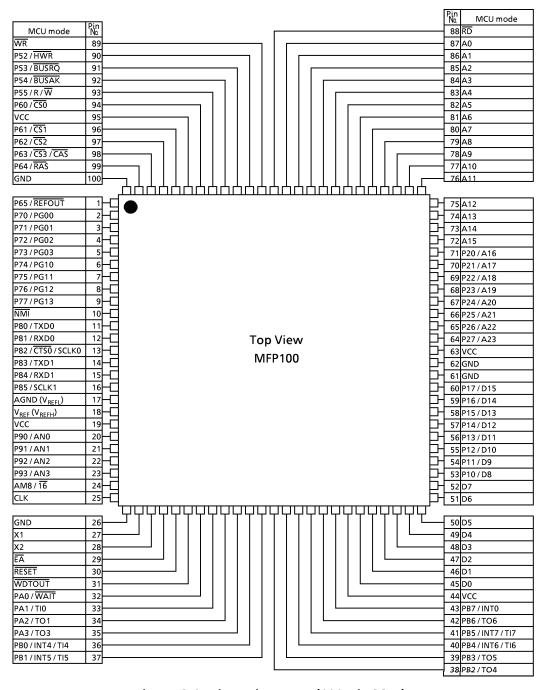

## 2. Pin Assignment and Functions

The assignment of input / output pins for TMP95C061B their name and outline functions are described below.

#### 2.1 Pin Assignment

Figure 2.1 shows pin assignment of TMP95C061B.

Figure 2.1 Pin Assignment (100-pin MFP)

#### 2.2 Pin Names and Functions

The names of input / output pins and their functions are described below. Table  $2.2\,$  Pin Names and Functions.

Table 2.2

| 14216 2.2                |                   |                  |                                                                                                                                                                                                                                        |  |  |  |  |

|--------------------------|-------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin name                 | Number<br>of pins | I/O              | Functions                                                                                                                                                                                                                              |  |  |  |  |

| D0 to D7                 | 8                 | I/O              | Data : 0 to 7 for data bus                                                                                                                                                                                                             |  |  |  |  |

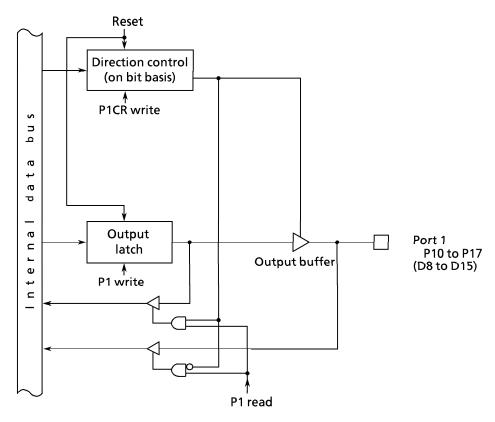

| P10 to P17<br>D8 to D15  | 8                 | I/O<br>I/O       | Port 1: I/O ports that allow I/O to be selected on a bit basis Data: 8 to 15 for data bus                                                                                                                                              |  |  |  |  |

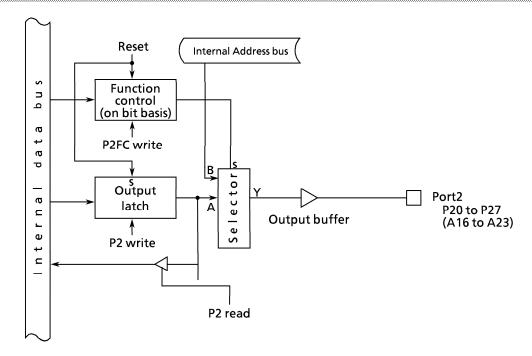

| P20 to P27<br>A16 to A23 | 8                 | Output<br>Output | Port 2 : Output ports<br>Address : 16 to 23 for address bus                                                                                                                                                                            |  |  |  |  |

| A8 to A15                | 8                 | Output           | Address : 8 to 15 for address bus                                                                                                                                                                                                      |  |  |  |  |

| A0 to A7                 | 8                 | Output           | Address : 0 to 7 for address bus                                                                                                                                                                                                       |  |  |  |  |

| RD                       | 1                 | Output           | Read : Strobe signal for reading external memory                                                                                                                                                                                       |  |  |  |  |

| WR                       | 1                 | Output           | Write : Strobe signal for writing data on pins D0 to 7                                                                                                                                                                                 |  |  |  |  |

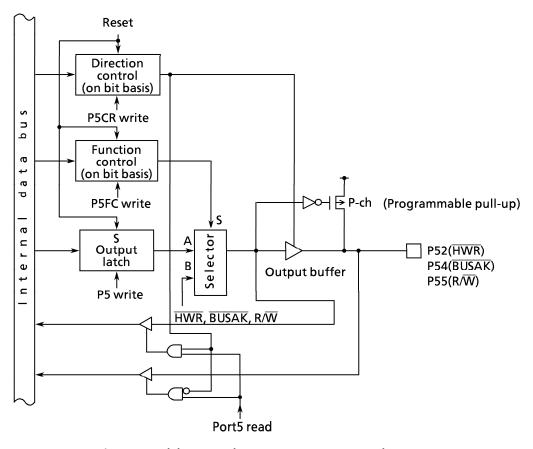

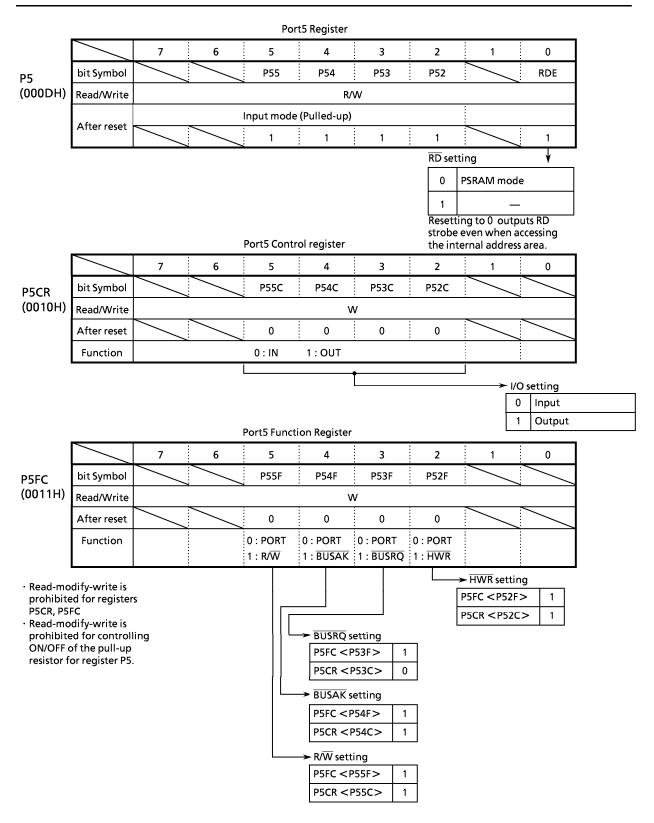

| P52<br>HWR               | 1                 | I/O<br>Output    | Port 52 : I/O port (with pull-up resistor) High Write : Strobe signal for writing data on pins D8 to 15                                                                                                                                |  |  |  |  |

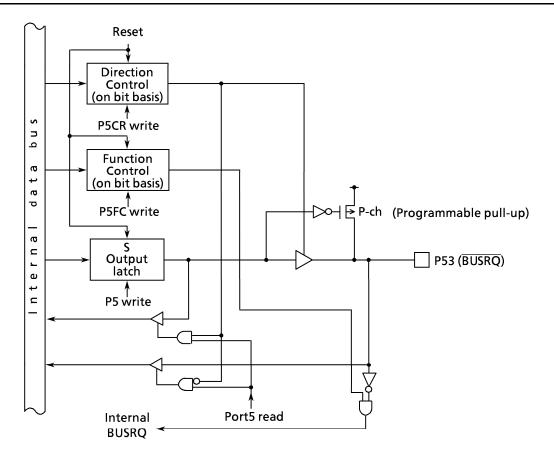

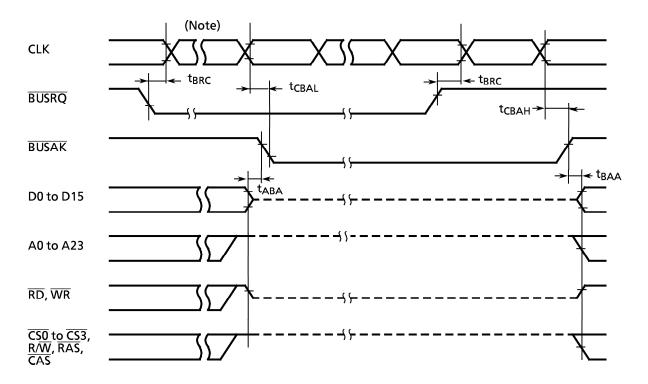

| P53<br>BUSRQ             | 1                 | I/O<br>Input     | Port 53 : I/O port (with pull-up resistor) Bus request : Signal used to request high impedance for D0 to 15, A0 to 23, RD, WR, HWR, R/W, CS0 to CS3, RAS, CAS and REFOUT (*) pins. (for external DMAC)                                 |  |  |  |  |

| P54<br>BUSAK             | 1                 | I/O<br>Output    | Port 54 : I/O port (with pull-up resistor)  Bus Acknowledge : Signal indicating that D0 to 15, A0 to 23, RD,  WR, HWR, R/W, CSO to CS3, RAS, CAS and  REFOUT (*) pins are at high impedance after receiving BUSRQ. (for external DMAC) |  |  |  |  |

| P55<br>R/W               | 1                 | I/O<br>Output    | Port 55 : Output port (with pull-up resistor) Read/Write : 1 : indicates read or dummy cycle 0 : indicates write cycle                                                                                                                 |  |  |  |  |

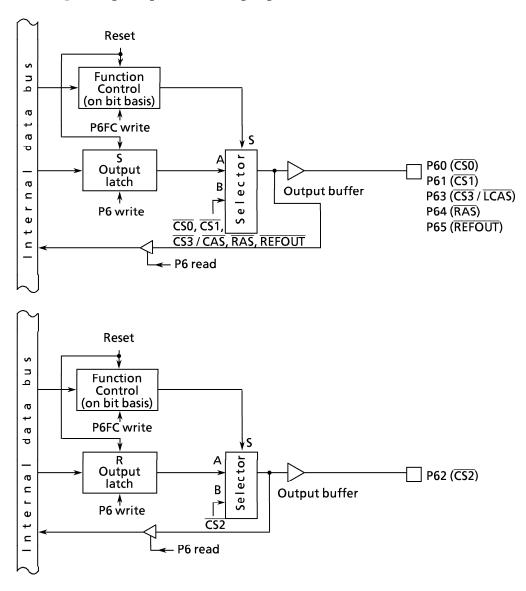

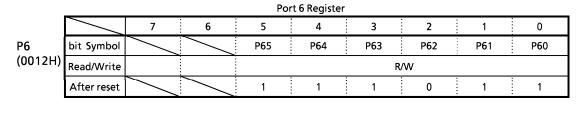

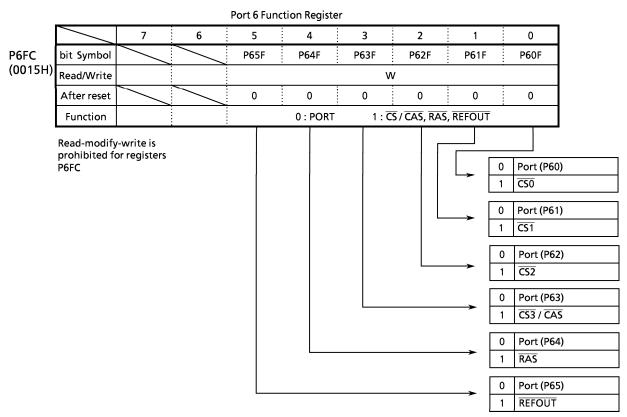

| P60<br>CS0               | 1                 | Output<br>Output | Port 60 : Output port Chip Select 0: Outputs 0 when address is within specified address area                                                                                                                                           |  |  |  |  |

| P61<br>CS1               | 1                 | Output<br>Output | Port 61 : Output port Chip Select 1: Output 0 when address is within specified address area                                                                                                                                            |  |  |  |  |

Note: With the external DMA controller, this device's built-in memory or built-in I/O cannot be accessed using the BUSRQ and BUSAK pins.

(\*) RAS, CAS, and REFOUT are set to high impedance only when bus release mode is set using the DRAM controller. For details, see 3.7, Dynamic RAM (DRAM) Controller.

| Pin name                   | Number<br>of pins | I/O                        | Functions                                                                                                                                                                                |

|----------------------------|-------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P62<br>CS2                 | 1                 | Output<br>Output           | Port 62 : Output port Chip Select 2: Outputs 0 if address is within specified address area                                                                                               |

| P63<br>CS3<br>CAS          | 1                 | Output<br>Output<br>Output | Port 63: Output port Chip Select 3: Outputs 0 if address is within specified address area Column address strobe: Outputs CAS strobe for DRAM if address is within specified address area |

| P64<br>RAS                 | 1                 | Output<br>Output           | Port 64 : Output port Low address strobe : Output RAS strobe for DRAM if address is within specified address area                                                                        |

| P65<br>REFOUT              | 1                 | Output<br>Output           | Port 65 : Output port<br>Refresh Output : 0 : indicates priod of refresh cycle                                                                                                           |

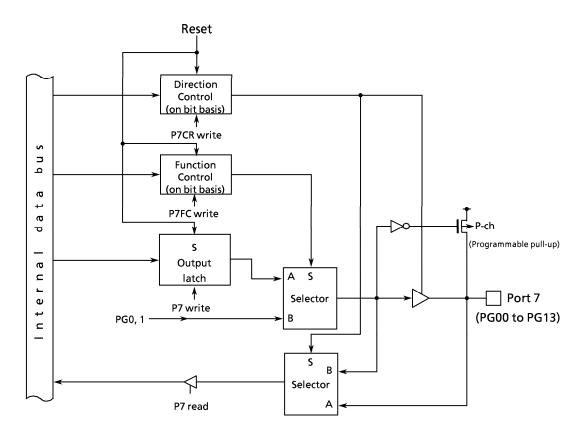

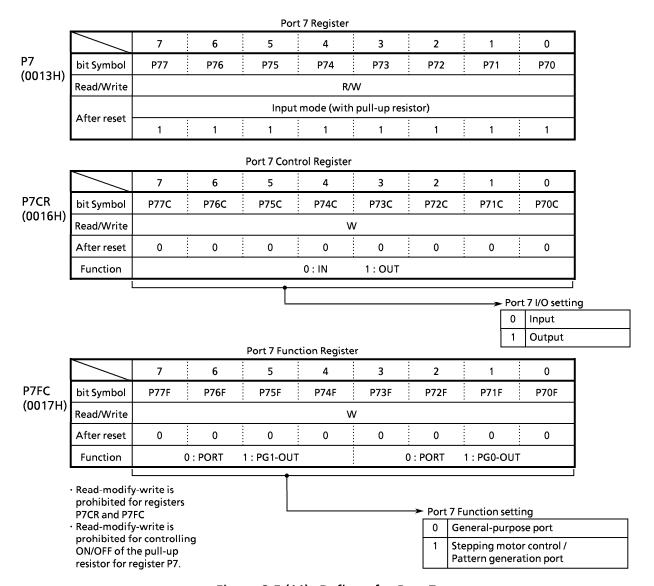

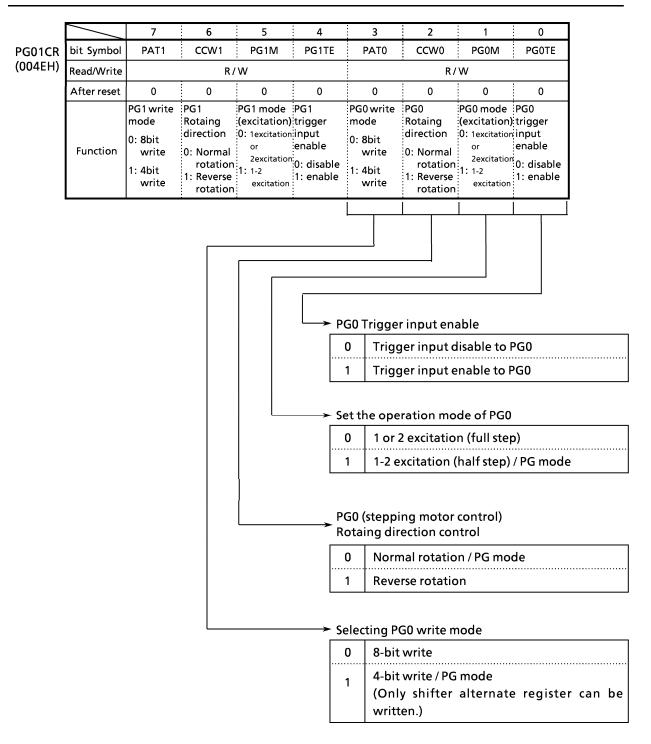

| P70 to P73<br>PG00 to PG03 | 4                 | I/O<br>Output              | Port 70 to 73: I/O port that allow selection of I/O on a bit basis (with pull-up resister)  Pattern generator Port : 00 to 03                                                            |

| P74 to P77<br>PG10 to PG13 | 4                 | I/O<br>Output              | Port 74 to 77: I/O port that allow selection of I/O on a bit basis (with pull-up resister)  Pattern generator Port : 10 to 13                                                            |

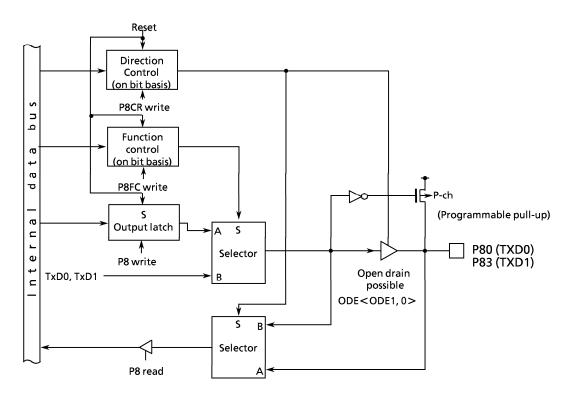

| P80<br>TXD0                | 1                 | I/O<br>Output              | Port 80 : I/O port (with pull-up resister)<br>Serial send data 0                                                                                                                         |

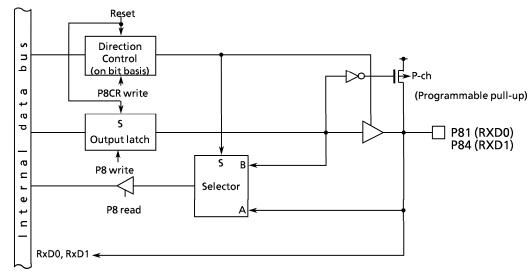

| P81<br>RXD0                | 1                 | I/O<br>Input               | Port 81 : I/O port (with pull-up resister) Serial receive data 0                                                                                                                         |

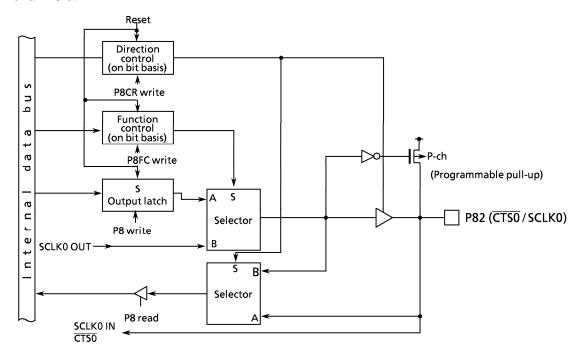

| P82<br>CTS0<br>SCLK0       | 1                 | I/O<br>Input<br>I/O        | Port 82 : I/O port (with pull-up resister) Serial data send enable (clear to send) Serial Clock I/O 0                                                                                    |

| P83<br>TXD1                | 1                 | I/O<br>Output              | Port 83 : I/O port (with pull-up resister) Serial send data 1                                                                                                                            |

| P84<br>RXD1                | 1                 | I/O<br>Input               | Port 84 : I/O port (with pull-up resister) Serial receive data 1                                                                                                                         |

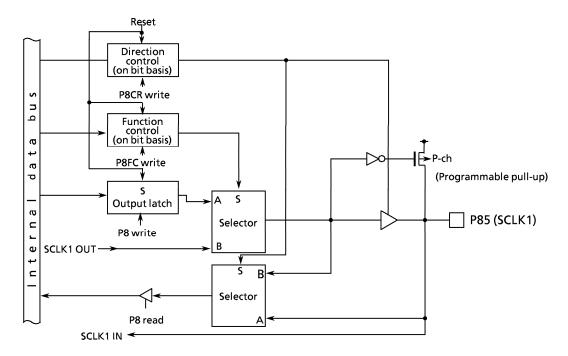

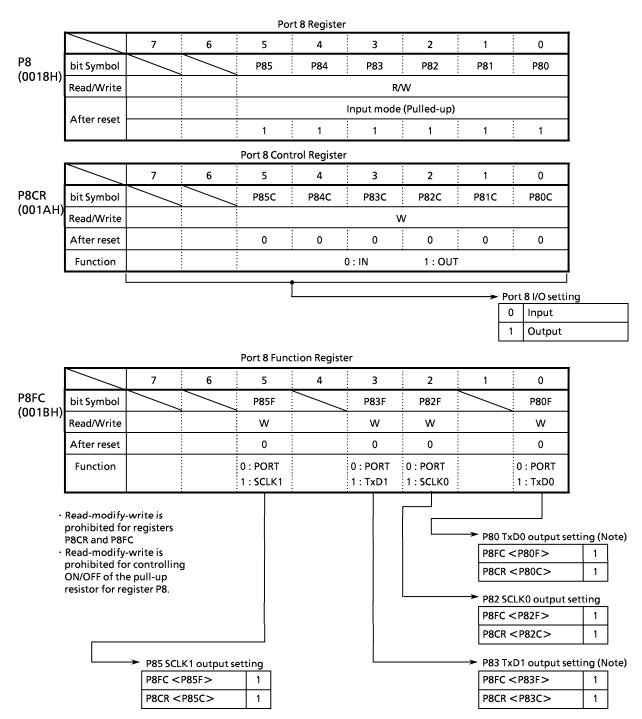

| P85<br>SCLK1               | 1                 | I/O<br>I/O                 | Port 85 : I/O port (with pull-up resister) Serial clock I/O 1                                                                                                                            |

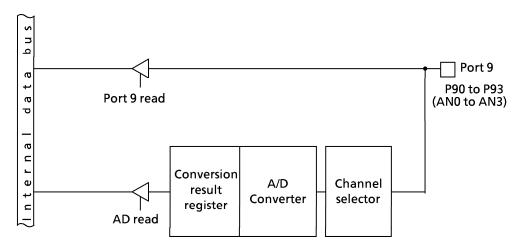

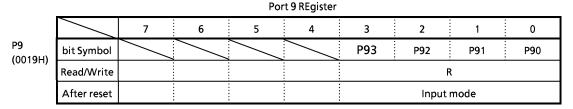

| P90 to P93<br>AN0 to AN3   | 4                 | Input<br>Input             | Port 9 : Input port<br>Analog input : Input to A/D converter                                                                                                                             |

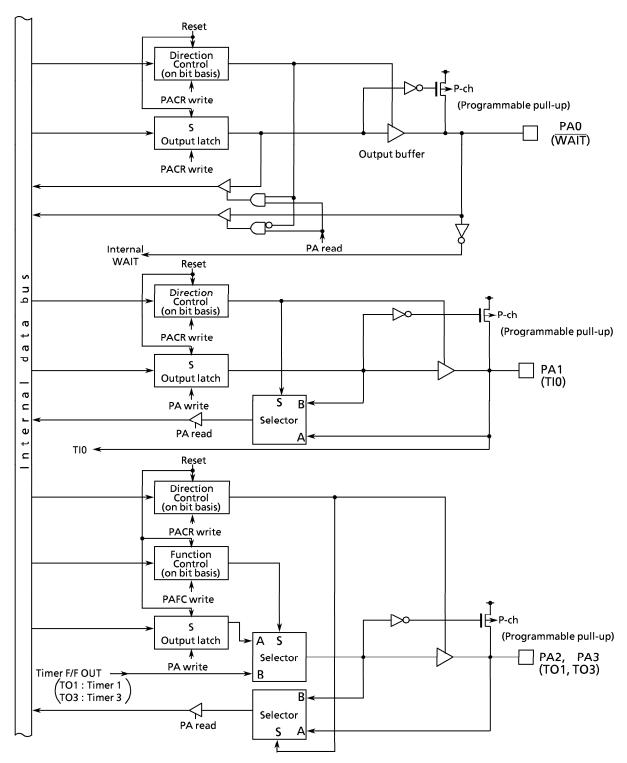

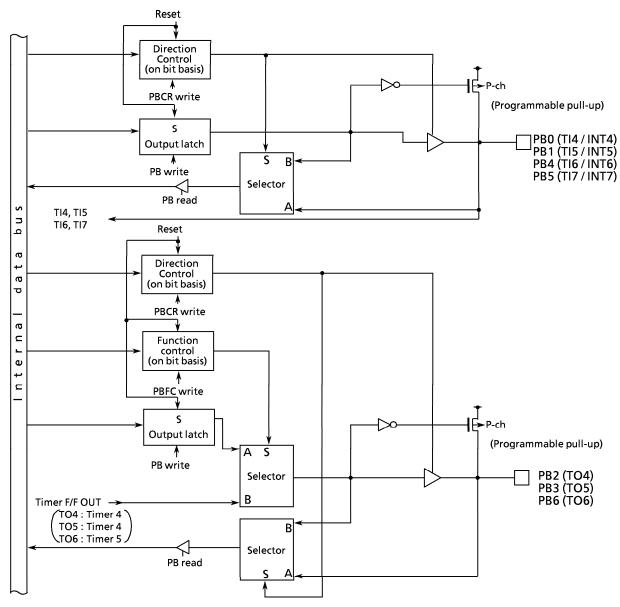

| PA0<br>WAIT                | 1                 | I/O<br>Input               | Port A0 : I/O port (with pull-up resister) Wait : Pin used to request CPU us wait                                                                                                        |

| PA1<br>TI0                 | 1                 | I/O<br>Input               | Port A1 : I/O port (with pull-up resister) Timer input 0 : Timer 0 input                                                                                                                 |

| PA2<br>TO1                 | 1                 | I/O<br>Output              | Port A2 : I/O port (with pull-up resister) Timer output 1 : Timer 0 or 1 output                                                                                                          |

| Pin name                              | Number<br>of pins | I/O                   | Functions                                                                                                                                                                                       |

|---------------------------------------|-------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PA3<br>TO3                            | 1                 | I/O<br>Output         | Port A3 : I/O port (with pull-up resistor) Timer output3 : Timer 2 or 3 output                                                                                                                  |

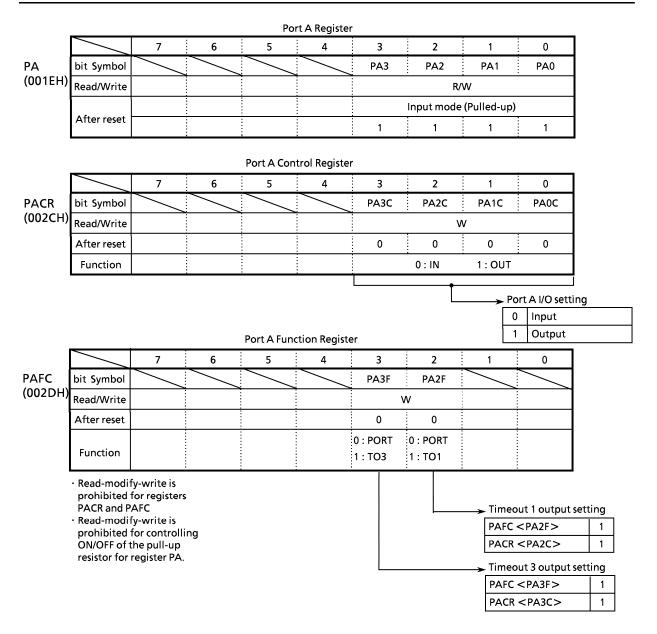

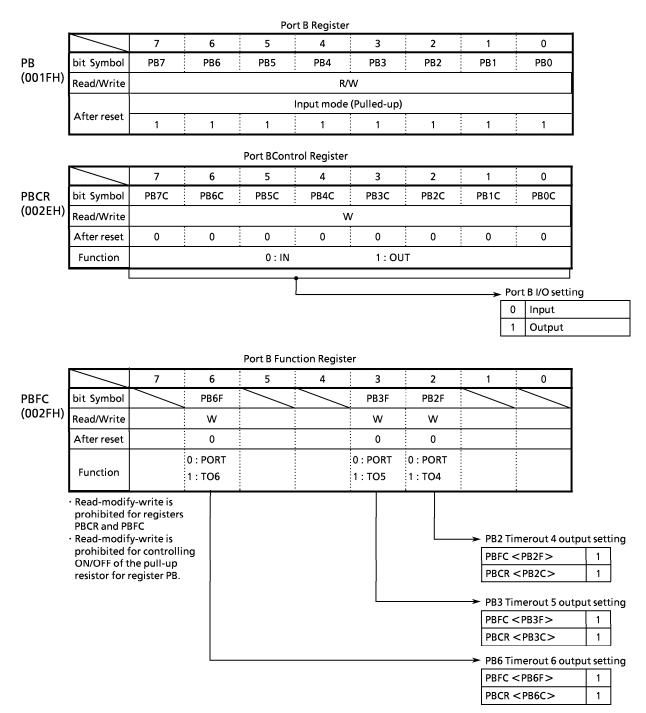

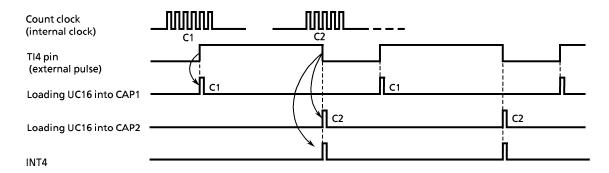

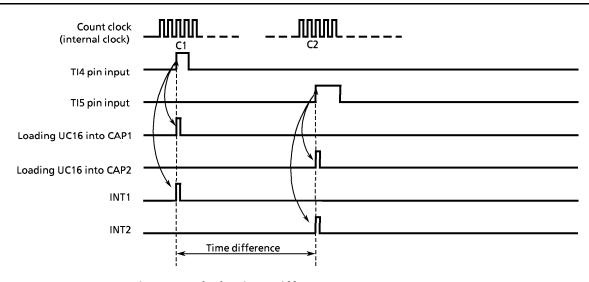

| PB0<br>TI4<br>INT4                    | 1                 | I/O<br>Input<br>Input | Port B0 : I/O port (with pull-up resistor) Timer input 4 : Timer 4 count / capture trigger signal input Interrupt request pin 4 : Interrupt request pin with programmable rising / falling edge |

| PB1<br>TI5<br>INT5                    | 1                 | I/O<br>Input<br>Input | Port 86 : I/O port (with pull-up resistor) Timer input 5 : Timer 4 count / capture trigger signal input Interrupt request pin 5 : Interrupt request pin with rising edge                        |

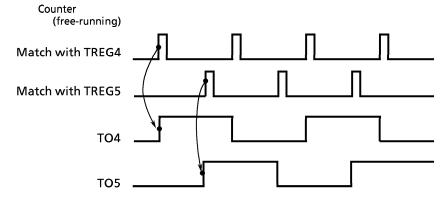

| PB2<br>TO4                            | 1                 | I/O<br>Output         | Port B2 : I/O port (with pull-up resistor) Timer output4 : Timer4 output                                                                                                                        |

| PB3<br>TO5                            | 1                 | I/O<br>Output         | Port B3 : I/O port (with pull-up resistor) Timer output5 : Timer4 output                                                                                                                        |

| PB4<br>TI6<br>INT6                    | 1                 | I/O<br>Input          | Port B4 : I/O port (with pull-up resistor) Timer input 6 : Timer 5 count / capture trigger signal input Interrupt request pin 6 : Interrupt request pin with progmnable rising / fulling edge   |

| PB5<br>TI7<br>INT7                    | 1                 | I/O<br>Input<br>Input | Port B5 : I/O port (with pull-up resistor) Timer input 7 : Timer 5 count / capture trigger signal input Interrupt request pin 7 : Interrupt request pin with rising edge                        |

| PB6<br>TO6                            | 1                 | I/O<br>Output         | Port B6 : I/O port (with pull-up resistor) Timer output6 : Timer5 output pin                                                                                                                    |

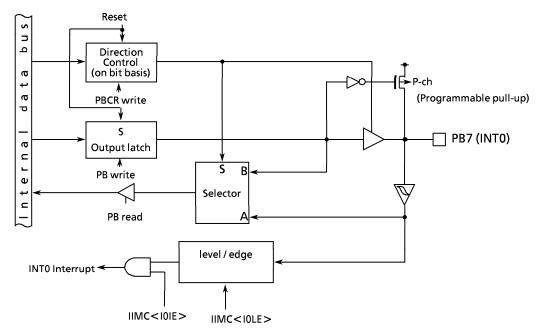

| PB7<br>INT0                           | 1                 | I/O<br>Input          | Port B7: I/O port (with pull-up resistor) Interrupt request pin 0: Interrupt request pin with progmmable level / rising edge                                                                    |

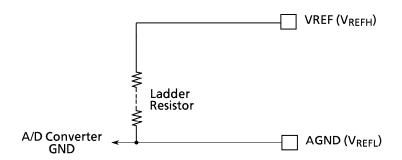

| V <sub>REF</sub> (V <sub>REFH</sub> ) | 1                 | Input                 | Pin for refereme voltage input to A/D connecter                                                                                                                                                 |

| AGND (V <sub>REFL</sub> )             | 7                 | Input                 | Ground pin for A/D converter                                                                                                                                                                    |

| WDTOUT                                | 1                 | Output                | Watchdog timer output pin                                                                                                                                                                       |

| NMI                                   | 1                 | Input                 | Non-maskable interrupt request pin : Interrupt request pin with falling edge. Can also be operated at rising edge by program.                                                                   |

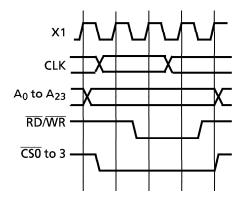

| CLK                                   | 1                 | Output                | Clock output : Outputs [external input clock X1 ÷ 4] clock. Pulled-up during reset.                                                                                                             |

| ĒĀ                                    | 1                 | Input                 | fixed GND                                                                                                                                                                                       |

| AM8/16                                | 1                 | Input                 | Address mode : Selects external Data Bus width "0" should be inputted with fixed 16 bit Bus width or 16 bit Bus interlorded with 8 bit Bus. "1" should be inputted with fixed 8 bit Bus width   |

| RESET                                 | 1                 | Input                 | Reset: Initializes LSI (with pull-up resister)                                                                                                                                                  |

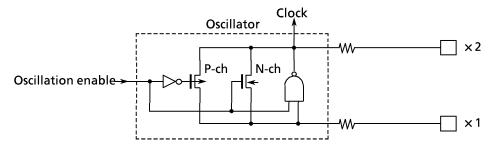

| X1 / X2                               | 2                 | I/O                   | Oscillator connecting pin                                                                                                                                                                       |

| vcc                                   | 4                 |                       | Power supply pin ( + 5 V) (All Vcc pins should be connected with the power supply pin.)                                                                                                         |

| VSS                                   | 4                 |                       | GND pin (0 V) (All Vss pins should be connected with GND (0 V).)                                                                                                                                |

Note 1: Pull-up resistor can be released from the pin by software.

Note 2: Connect all VCC pins to power supply and all VSS pins to GND.

## 3. Operation

This section describes in blocks the functions and basic operations of TMP95C061B devices.

Check the \[ \frac{7}{.}\] Care Points and Restriction \[ \] because of the Care Points etc are described.

#### 3.1 CPU

TMP95C061B devices has a built-in high-performance 16-bit CPU (900/H CPU). (For CPU operation, see TLCS-900 CPU in the previous section).

This section describes CPU functions unique to TMP95C061B that are not described in the previous section.

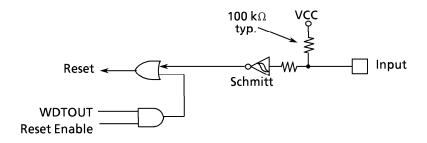

#### 3.1.1 Reset

To reset the TMP95C061B, the  $\overline{RESET}$  input must be kept at 0 for at least 10 system clocks (10 states: 0.8  $\mu s$  at 25 MHz) within an operating voltage range and with a stable oscillation.

When reset is accepted, the CPU sets as follows:

• Program Counter (PC) according to Reset Vector that is stored 0FFFF00H to 0FFFF02H.

```

PC (7:0) \leftarrow stored data to 0FFFF00H

PC (15:8) \leftarrow stored data to 0FFFF01H

PC (23:16) \leftarrow stored data to 0FFFF02H

```

- Stack pointer (XSP) for system mode to 100H.

- IFF2 to 0 bits of status register to 111. (Sets mask register to interrupt level 7.)

- Sets the MAX bit of the status register (SR) to 1 (this sets maximum mode).

(Note: This product does not support minimum mode. Do not use the MIN instruction.)

• Bits RFP2 to 0 of status register to 000. (Sets register banks to 0.)

When reset is released, instruction execution starts from PC (reset vector). CPU internal registers other than the above are not changed.

When reset is accepted, processing for built-in I/Os, ports, and other pins is as follows

- Initializes built-in I/O registers as per specifications.

- Sets port pins (including pins also used as built-in I/Os) to general-purpose input / output port mode.

- Sets the WDTOUT pin to 0. (Watchdog timer is set to enable after reset.)

- Pulls up the CLK pin to 1.

95C061B-8 2003-03-31

## 3.1.2 External data width selection pin (AM8 / $\overline{16}$ )

After Reset operation, TMP95C061B operates 8 bits or 16 bits external data width according to input to AM8 /  $\overline{16}$  pin.

- In case with fixed 16 bit bus or 16 bit bus interlarded with 8 bit bus "0" should be inputted. In this case, Port 1 (P10 to P17) operate as data bus D8 to 15. The data bus width for external access is set by Chip Select / Wait Control resister.

- In case with fixed 8 bit bus

"1" should be inputted. In this case, Port 1 (P10 to P17) operate as 8 bit I/O ports.

And the value set in Chip Select / Wait Control resister < B0BUS>, < B1BUS>,

<B2BUS>, < B3BUS> and < BEXBUS> are neglected.

95C061B-9 2003-03-31

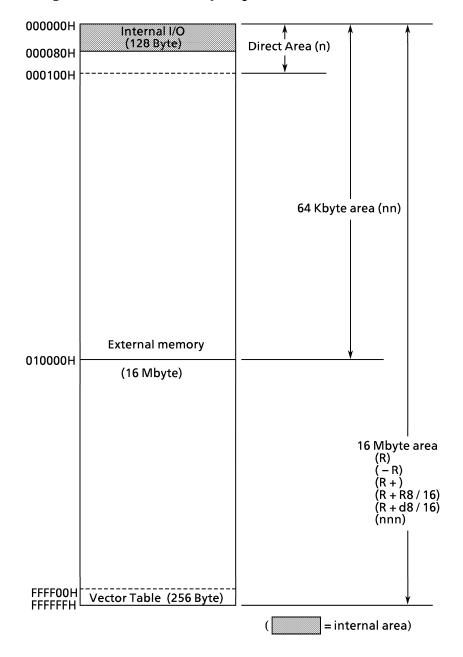

## 3.2 Memory Map

Figure 3.2 shows a memory map of the TMP95C061B.

Note: After reset operation, Stack point (XSP) is set to 100H.

Figure 3.2 Memory Map

## 3.2.1 Operation at internal I/O area access

TMP95C061B uses 128 bytes of address space (0H to 7FH) as an internal I/O area. Internal I/O registers are mapped on this area.

Operation of the internal I/O area access is different from that of the other address area access about following two points.

(1) In the internal I/O area access,  $\overline{RD}$ , and  $\overline{WR}$  ( $\overline{HWR}$ ) strobe signals are nonactive and fixed to high level.

However, in PSRAM mode set by P5 < RDE > register,  $\overline{\text{RD}}$  strobe signal becomes active also in the internal I/O area access. (See 3.5.3 Port5 (P52 to P55).)

(2) In the internal I/O area access, the number of waits becomes zero or one depending on the internal state of the CPU. This wait can't be controlled by chip select / wait controller (see 3.6 Chip Select / Wait Controller, AM8/ $\overline{16}$  pin). When the specified address area overlaps with the internal I/O area, the operation as the internal I/O area takes priority of the specified address area.

#### 3.3 Interrupts

TLCS-900 interrupts are controlled by the CPU interrupt mask flip-flop (IFF2 to 0) and the built-in interrupt controller.

TMP95C061B has the following 26 interrupt sources:

- Interrupts from the CPU…2 (Software interrupts, and Illegal (undefined) instruction execution)

- $\bullet$  Interrupts from external pins (\$\overline{NMI}\$, INT0, and INT4 to 7)\$\cdots\$6

- Interrupts from built-in I/Os···14

- Interrupts from micro DMA···4

A fixed individual interrupt vector number is assigned to each interrupt source; six levels of priority (variable) can also be assigned to each maskable interrupt. Non-maskable interrupts have a fixed priority of 7.

When an interrupt is generated, the interrupt controller sends the value of the priority of the interrupt source to the CPU. When more than one interrupt is generated simultaneously, the interrupt controller sends the value of the highest priority (7 for non-maskable interrupts is the highest) to the CPU.

The CPU compares the value of the priority sent with the value in the CPU interrupt mask register (IFF2 to 0). If the value is higher or equal to that of the CPU interrupt mask register, the interrupt is accepted. However, software interrupts and illegal instruction interrupts generated by the CPU are processed without comparison with the IFF<2:0>value.

The value in the CPU interrupt mask register (IFF2 to 0) can be changed using the EI instruction (contents of the EI num/IFF<2:0> = num). For example, programming EI 3 enables acceptance of maskable interrupts with a priority of 3 or greater, and non-maskable interrupts which are set in the interrupt controller. The DI instruction (IFF<2:0> = 7) operates in the same way as the EI 7 instruction. Since the priority values for maskable interrupts are 0 to 6, the DI instruction is used to disable maskable interrupts to be accepted. The EI instruction becomes effective immediately after execution. (With the TLCS-90, the EI instruction becomes effective after execution of the subsequent instruction.)

In addition to the general-purpose interrupt processing mode described above, there is also micro DMA processing mode. Micro DMA is a mode used by the CPU to automatically transfer byte, word and 4-byte data. It enables the CPU to process interrupts such as data saves to built-in I/Os at high speed.

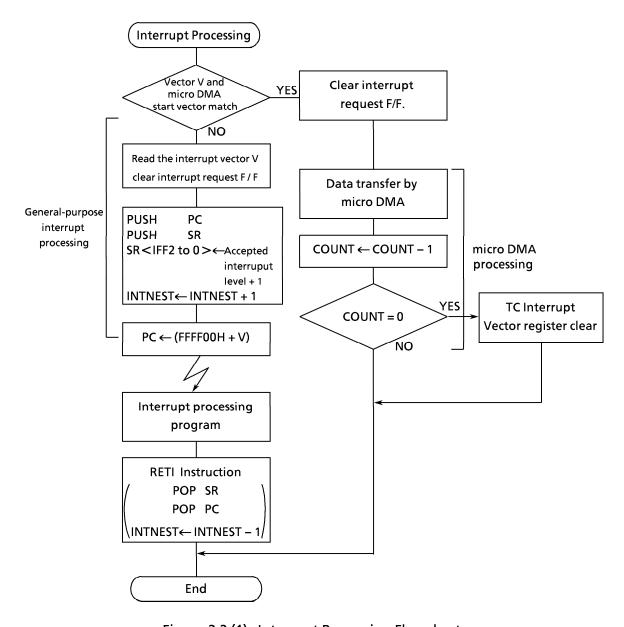

Figure 3.3 (1) is a flowchart showing overall interrupt processing.

Figure 3.3 (1) Interrupt Processing Flowchart

### 3.3.1 General-Purpose Interrupt Processing

When accepting an interrupt, the CPU operates as follows:

However, in the case of software interrupts and illegal instruction interrupts generated by the CPU, the CPU skips (1) and (3) and executes steps (2), (4), and (5).

- (1) The CPU reads the interrupt vector from the interrupt controller. When more than one interrupt with the same level is generated simultaneously, the interrupt controller generates interrupt vectors in accordance with the default priority (which is fixed as follows: the smaller the vector value, the higher the priority), then clears the interrupt request.

- The CPU pushes the program counter and the status register to the system stack area (area indicated by the system mode stack pointer (XSP)).

- (3) The CPU sets a value in the CPU interrupt mask register <IFF2 to 0> that is higher by 1 than the value of the accepted interrupt level. However, if the value is 7, 7 is set without an increment.

- (4) The CPU increments the INTNEST (Interrupt Nesting Counter).

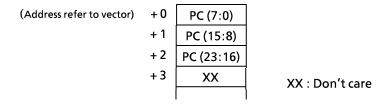

- (5) The CPU jumps to address stored at FFFF00H + interrupt vector, then starts the interrupt processing routine.

| The following diagra | m choszcall t    | ha ahowa nrocaccin  | a etata numbar  |

|----------------------|------------------|---------------------|-----------------|

| The following diagra | iii siiows air t | are above processin | g state number. |

| Bus Width of<br>Stack Area | Bus Width of Interrupt<br>Vector Area | Interrupt processing state number |

|----------------------------|---------------------------------------|-----------------------------------|

| 8 bit                      | 8 bit                                 | 28                                |

| 8 511                      | 16 bit                                | 24                                |

| 16 bit                     | 8 bit                                 | 22                                |

|                            | 16 bit                                | 18                                |

To return to the main routine after completion of the interrupt processing, the RETI instruction is usually used. Executing this instruction restores the contents of the program counter and the status registers and decrements INTNEST (Interrupt Nesting Counter).

Though acceptance of non-maskable interrupts cannot be disabled by program, acceptance of maskable interrupts can. A priority can be set for each source of maskable interrupts. The CPU accepts an interrupt request with a priority higher or equal to the value in the CPU mask register <IFF2 to 0>. The CPU mask register <IFF2 to 0> is set to a value higher by 1 than the priority of the accepted interrupt. Thus, if an interrupt with a level higher than the interrupt being processed is generated, the CPU accepts the interrupt with the higher level, causing interrupt processing to nest.

If an interrupt generated while the CPU is performing processes (1) to (5) for an earlier interrupt, the new interrupt is sampled immediately after the start instruction of the interrupt processing routine is executed. Setting DI as the start instruction disables maskable interrupt nesting. (Note: With the 900 and 900/L, an interrupt is sampled before the start instruction is executed.)

Resetting initializes the CPU mask registers <IFF2 to 0> to 7; therefore, maskable interrupts are disabled.

The addresses 0FFFF00H to 0FFFFFFH (256 bytes) of the TMP95C061B are assigned for interrupt vector area.

Table 3.3 (1) TMP95C061B Interrupt Table

|               | Tables.3 (1) TWP95C061B Interrupt Table |                                         |                     |                      |              |  |  |  |  |

|---------------|-----------------------------------------|-----------------------------------------|---------------------|----------------------|--------------|--|--|--|--|

| Default       | Туре                                    | Interrupt source                        | Vector value<br>"V" | Address refer        | Micro DMA    |  |  |  |  |

| priority<br>1 | 71: -                                   | Reset, or SWI0 instruction              | 0 0 0 0 H           | to vector<br>FFFF00H | start vector |  |  |  |  |

| 2             |                                         | SWI 1 instruction                       | 0 0 0 0 H           | FFFF04H              | _            |  |  |  |  |

| 3             |                                         |                                         |                     |                      | _            |  |  |  |  |

|               |                                         | INTUNDEF: Illegal instruction, or SWI2  | 0 0 0 8 H           | FFFF08H              | _            |  |  |  |  |

| 4             | Non-                                    | SWI 3 instruction                       | 0 0 0 C H           | FFFF0CH              | _            |  |  |  |  |

| 5             | maskable                                | SWI 4 instruction                       | 0 0 1 0 H           | FFFF10H              | -            |  |  |  |  |

| 6             |                                         | SWI 5 instruction                       | 0 0 1 4 H           | FFFF14H              | -            |  |  |  |  |

| 7             |                                         | SWI 6 instruction                       | 0 0 1 8 H           | FFFF18H              | _            |  |  |  |  |

| 8             |                                         | SWI 7 instruction                       | 0 0 1 C H           | FFFF1CH              | _            |  |  |  |  |

| 9             |                                         | NMI Pin                                 | 0 0 2 0 H           | FFFF20H              | -            |  |  |  |  |

| 10            |                                         | INTWD : Watchdog timer                  | 0024H               | FFFF24H              | _            |  |  |  |  |

| _             |                                         | (Micro DMA)                             |                     |                      | - I          |  |  |  |  |

| 11            |                                         | INTO pin                                | 0 0 2 8 H           | FFFF28H              | 0AH          |  |  |  |  |

| 12            |                                         | INT4 pin                                | 0 0 2 C H           | FFFF2CH              | 0BH          |  |  |  |  |

| 13            |                                         | INT5 pin                                | 0 0 3 0 H           | FFFF30H              | 0CH          |  |  |  |  |

| 14            |                                         | INT6 pin                                | 0 0 3 4 H           | FFFF34H              | 0DH          |  |  |  |  |

| 15            |                                         | INT7 pin                                | 0 0 3 8 H           | FFFF38H              | 0EH          |  |  |  |  |

| -             |                                         | (Reserved)                              | 0 0 3 C H           | FFFF3CH              | -            |  |  |  |  |

| 16            |                                         | INTTO : 8-bit timer0                    | 0 0 4 0 H           | FFFF40H              | 10H          |  |  |  |  |

| 17            |                                         | INTT1 : 8-bit timer1                    | 0 0 4 4 H           | FFFF44H              | 11H          |  |  |  |  |

| 18            |                                         | INTT2 : 8-bit timer2                    | 0 0 4 8 H           | FFFF48H              | 12H          |  |  |  |  |

| 19            |                                         | INTT3 : 8-bit timer3                    | 0 0 4 C H           | FFFF4CH              | 13H          |  |  |  |  |

| 20            | Maskable                                | INTTR4 : 16-bit timer4 (TREG4)          | 0 0 5 0 H           | FFFF50H              | 14H          |  |  |  |  |

| 21            |                                         | INTTR5 : 16-bit timer4 (TREG5)          | 0 0 5 4 H           | FFFF54H              | 15H          |  |  |  |  |

| 22            |                                         | INTTR6 : 16-bit timer5 (TREG6)          | 0 0 5 8 H           | FFFF58H              | 16H          |  |  |  |  |

| 23            |                                         | INTTR7 : 16-bit timer5 (TREG7)          | 0 0 5 C H           | FFFF5CH              | 17H          |  |  |  |  |

| 24            |                                         | INTRX0 : Serial receive (Channel.0)     | 0060H               | FFFF60H              | 18H          |  |  |  |  |

| 25            |                                         | INTTX0 : Serial send (Channel.0)        | 0064H               | FFFF64H              | 19H          |  |  |  |  |

| 26            |                                         | INTRX1 : Serial receive (Channel.1)     | 0068H               | FFFF68H              | 1AH          |  |  |  |  |

| 27            |                                         | INTTX1 : Serial send (Channel.1)        | 006CH               | FFFF6CH              | 1BH          |  |  |  |  |

| 28            |                                         | INTAD : A/D conversion completion       | 0070H               | FFFF70H              | 1CH          |  |  |  |  |

| 29            |                                         | INTTC0 Micro DMA completion (channel.0) | 0074H               | FFFF74H              | _            |  |  |  |  |

| 30            |                                         | INTTC1 Micro DMA completion (channel.1) | 0078H               | FFFF78H              | - <b> </b>   |  |  |  |  |

| 31            |                                         | INTTC2 Micro DMA completion (channel.2) | 0 0 7 C H           | FFFF7CH              | _            |  |  |  |  |

| 32            |                                         | INTTC3 Micro DMA completion (channel.3) | 0 0 8 0 H           | FFFF80H              | _            |  |  |  |  |

| _             |                                         | (Reserved)                              | 0084H               | FFFF84H              | _            |  |  |  |  |

| to            |                                         | to                                      | to                  | to                   | to           |  |  |  |  |

| _             |                                         | (Reserved)                              | 0 0 F C H           | FFFFFCH              | _            |  |  |  |  |

## Setting to Reset / Interrupt Vector

## ① Reset Vector

## ② Interrupt Vector (except Reset Vector)

## (Setting Example)

$Reset\ Vector: 8100H, \overline{NMI}\ Vector: 9ABCH, INTAD\ Vector: 123456h.$

| ORG  | 8100H           |                                          |

|------|-----------------|------------------------------------------|

| LD . | A, B            | (cf)                                     |

|      |                 | ORG, DL are the Assembler Directive.     |

| ORG  | 9ABCH           | ORG: control location counter            |

| LD   | В, С            | DL : define the long word (32 bits) data |

|      |                 |                                          |

| ORG  | 123456H         |                                          |

| LD . | C, A            |                                          |

|      |                 |                                          |

| ORG  | OFFFF00H        |                                          |

| DL   | <u>008100</u> H | ; Reset = 8100H                          |

|      |                 |                                          |

| ORG  | 0FFFF20H        |                                          |

| DL   | <u>009ABC</u> H | ; NMI = 9ABCH                            |

|      |                 |                                          |

| ORG  | OFFFF70H        |                                          |

| DL   | <u>123456</u> H | ; INTAD = 123456H                        |

#### 3.3.2 Micro DMA

In addition to conventional interrupt processing, TMP95C061B supports the micro DMA function. For interrupt requests set for micro DMA, micro DMA processing is performed at the highest priority for maskable interrupts (level 6), regardless of the actual interrupt level set for the interrupt.

Because the function of micro DMA has been implemented with the cooperative operation of CPU, when CPU is a state of stand-by by HALT instruction, the requirement of micro DMA will be ignored (pending).

## (1) Micro DMA Operation

When an interrupt request occurs for an interrupt specified by the micro DMA start vector register, micro DMA sends the micro DMA request to the CPU with the highest priority for maskable interrupts (level 6), regardless of the actual interrupt level set for the interrupt, and starts micro DMA. The micro DMA function has four channels. This allows micro DMA to be set for up to four interrupts at the same time.

When micro DMA is accepted, the interrupt request F-F for the micro DMA channel is cleared, data are automatically transferred from the transfer source address to the transfer destination address (the addresses are set in the control register), and the transfer count is decremented. If the decremented result is other than zero, micro DMA processing terminates. If the decremented result is zero, the CPU sends a micro DMA transfer end interrupt (INTTCn) to the interrupt controller, clears the micro DMA start vector register to 0, disables the next micro DMA startup, and terminates micro DMA processing.

If an interrupt request for the interrupt source used is received between the time that the micro DMA start vector is cleared and the time that it is reset, the CPU performs general-purpose processing at the specified interrupt level. Therefore, if the interrupt source is only being used for starting micro DMA (not used as an interrupt), set the interrupt level to zero.

When simultaneously using the same interrupt resource for both the micro DMA and general-purpose interrupts as described above, set the level of the interrupt source used to start micro DMA lower than the levels of all other interrupt sources. In this case, the cause of general interrupt is limited to the edge interrupt.

Example : When using timers 0 to 3 for running micro DMA 0 to 3

Set the interrupt level of timers 0 to 3 to 1

Set other interrupt levels to 2 to 6

Like other maskable interrupts, the priority of the micro DMA transfer end interrupt is determined by the interrupt level and default priority.

If multiple-channel micro DMA requests occur at the same time, the priority is determined by the channel numbers, not the interrupt levels. The lower the channel number, the higher the priority.  $(CH0 \text{ (high)} \rightarrow CH3 \text{ (low)})$

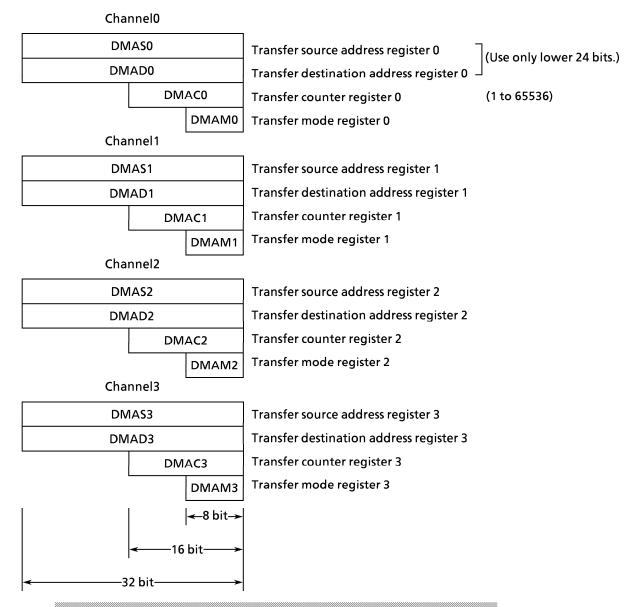

The transfer source and transfer destination addresses are set in 32-bit control registers. However, as only 24-bit addresses are output, the address space available to micro DMA is 16M bytes.

Three transfer modes are supported: 1-byte transfer, 1-word transfer (= two bytes), and 4-byte transfer. For each transfer mode, it is possible to specify whether to increment, decrement, or fix source and destination addresses after transfer. These modes facilitate data transfer from I/O to memory, from memory to I/O, and from I/O to I/O. For transfer mode details, see "Transfer Mode Register Details" later in this manual.

As a 16-bit transfer counter is used, micro DMA can perform a maximum of 65536 transfers (initializing the counter to 0000H specifies the maximum number of transfers).

The 18 interrupt sources with micro DMA start vectors (as listed in Table 3.3 (1)) can be used to start micro DMA processing.

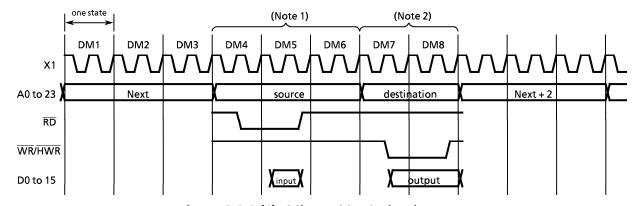

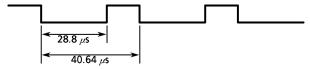

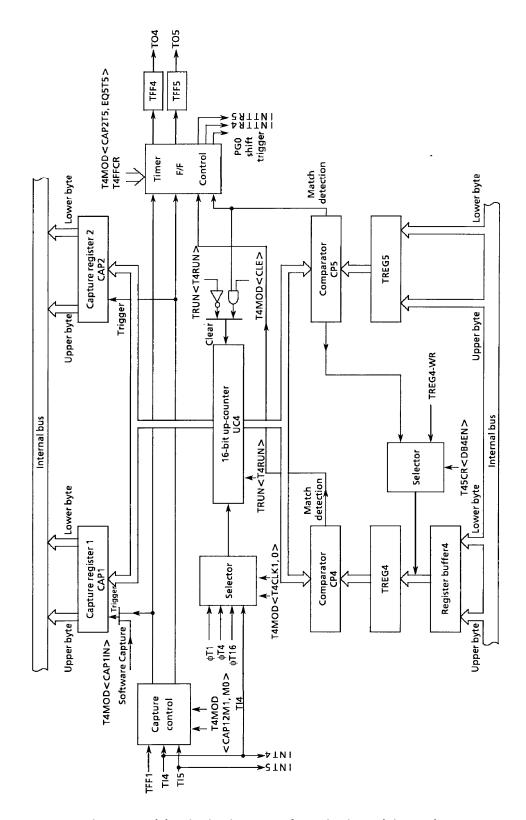

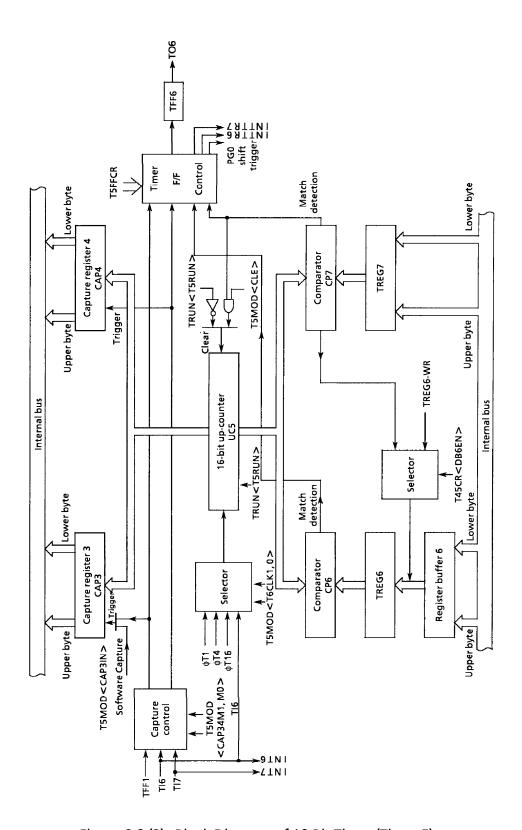

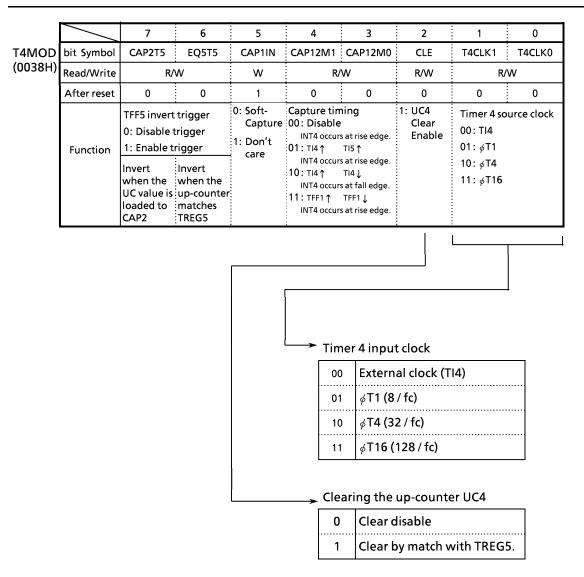

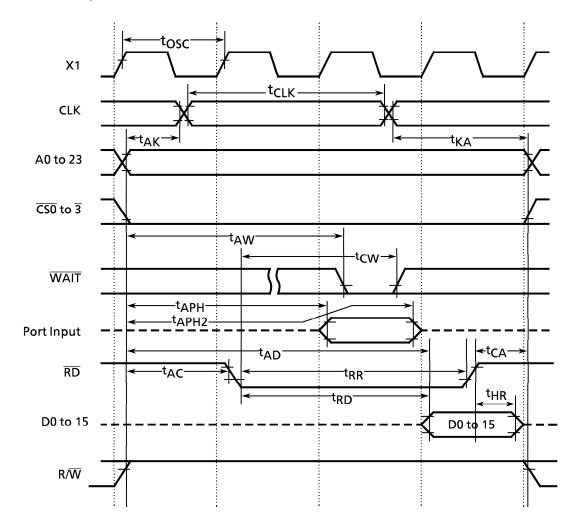

Figure 3.3.2 (1) shows the micro DMA cycle for 1-word transfer in transfer destination address INC mode (the same apart from counter mode). (The conditions for this cycle are based on a 16-bit bus, 0 waits, and transfer source/transfer destination addresses both even-numbered values.).

Figure 3.3.2 (1) Micro DMA Cycle Diagram

States 1 to 3: Instruction fetch cycle (prefetches the next instruction code)

If the instruction cue buffer has three or more bytes of instruction code, the cycles are dummy cycles.

States 4 to 5 : Micro DMA read cycles

State 6 : Dummy cycle (address bus remains the same as in state 5)

States 6 to 8: Micro DMA write cycle

Note 1: If the source address area uses an 8-bit bus, two states are added.

If also the source address area uses a 16-bit bus and the source address is an oddnumbered address, two states are added.

Note 2: If the destination address area uses an 8-bit bus, two states are added.

If also the destination address area uses a 16-bit bus and the destination address is an odd-numbered address, two states are added.

### (2) Register configuration (CPU control register)

These Control Register can not be set only "LDC cr, r" instruction.

#### Transfer mode register details (3)

(1 states = 80 ns at 25 MHz)

Note: n: corresponds to micro DMA channels 0 to 3.

> DMADn + / DMASn + : Post-increment (Increments register value after transfer.) DMADn -/ DMASn -: Post-decrement (Decrement register value after transfer.)

"I/O" means the fixed address, "memory" means the increased or decreased address in this

table.

Do not use undefined codes for transfer mode control.

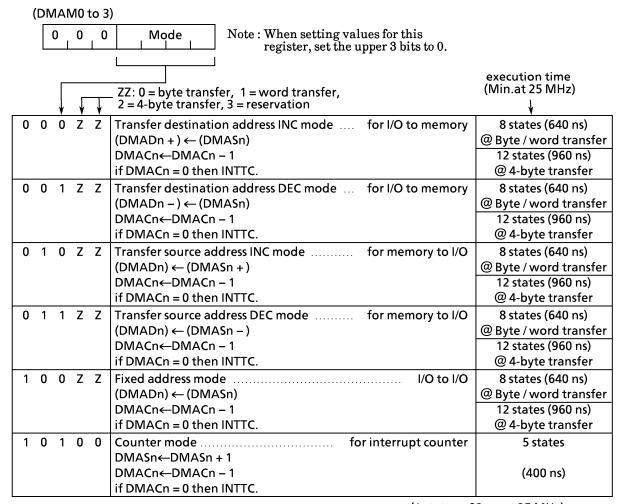

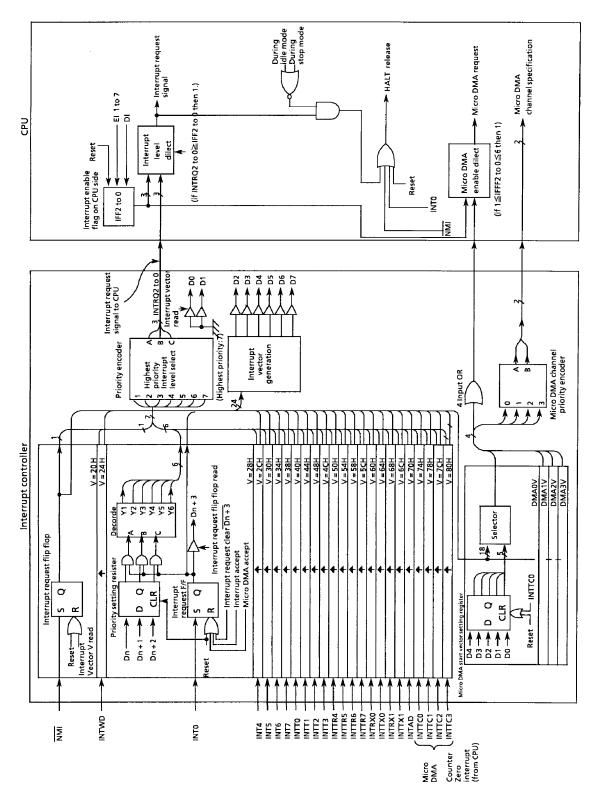

#### 3.3.3 Interrupt Controller

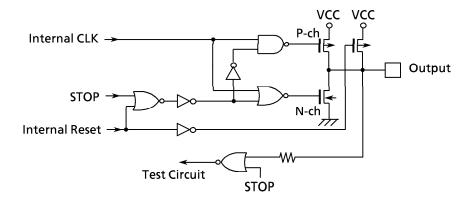

Figure 3.3.3 (1) is a block diagram of the interrupt circuits. The left half of the diagram shows the interrupt controller; the right half includes the CPU interrupt request signal circuit and the HALT release signal circuit.

Each interrupt channel (total of 24 channels) in the interrupt controller has an interrupt request flip-flop, interrupt priority setting register, and a register for storing the micro DMA start vector. The interrupt request fip-flop is used to latch interrupt requests from peripheral devices. The flip-flop is cleared to 0 at reset, when the CPU reads the interrupt channel vector after the acceptance of interrupt, when the CPU accepts the micro DMA request or when the CPU executes an instruction that clears the interrupt of that channel (writes 0 in the clear bit of the interrupt priority setting register).

For example, to clear the INTO interrupt request, set the register after the DI instruction as follows.

$INTEOAD \leftarrow ---- 0 --- Zero-clears the INTO Flip Flop.$

The status of the interrupt request flip-flop is detected by reading the clear bit. Detects whether there is an interrupt request for an interrupt channel.

The interrupt priority can be set by writing the priority in the interrupt priority setting register (eg, INTE0AD, INTE45, etc.) provided for each interrupt source. Interrupt levels to be set are from 1 to 6. Writing 0 or 7 as the interrupt priority disables the corresponding interrupt request. The priority of the non-maskable interrupt ( $\overline{\text{NMI}}$  pin, watchdog timer, etc.) is fixed to 7. If interrupt requests with the same interrupt level are generated simultaneously, interrupts are accepted in accordance with the default priority (the smaller the vector value, the higher the priority).

The interrupt controller sends the interrupt request with the highest priority among the simultaneous interrupts and its vector address to the CPU. The CPU compares the interrupt mask register <IFF2 to 0> set in the Status Register by the interrupt request signal with the priority value sent; if the latter is higher, the interrupt is accepted. Then the CPU sets a value higher than the priority value by 1 in the CPU SR<IFF2 to 0>. Interrupt requests where the priority value equals or is higher than the set value are accepted simultaneously during the previous interrupt routine. When interrupt processing is completed (after execution of the RETI instruction), the CPU restores the valve in the interrupt mask register saved in the stack before the interrupt was generated to the CPU SR<IFF2 to 0>.

The interrupt controller also has four registers used to store the micro DMA start vector. These are I/O registers; unlike other micro DMA registers (DMAS, DMAD, DMAM, and DMAC). Writing the start vector of the interrupt source for the micro DMA processing (see Table 3.3.(1)), enables the corresponding interrupt to be processed by micro DMA processing. The values must be set in the micro DMA parameter registers (eg, DMAS and DMAD) prior to the micro DMA processing.

Figure 3.3.3 (1) Block Diagram of Interrupt Controller

## (1) Interrupt priority setting register

(Read-modify-write is prohibited.)

| Symbol   | Address  | 7                                                                             | 6                                            | 5               | 4              | 3           | 2          | 1          | . 0         |                   |

|----------|----------|-------------------------------------------------------------------------------|----------------------------------------------|-----------------|----------------|-------------|------------|------------|-------------|-------------------|

|          |          |                                                                               | INT                                          | AD              |                | INTO        |            |            |             | ←Interrupt source |

| INTE0AD  | 0070H    | IADC                                                                          | IADM2                                        | IADM1           | IADM0          | IOC         | 10M2       | IOM1       | IOM0        | ←bit Symbol       |

| INTEUAD  | 0070H    | R/W                                                                           |                                              | W               |                | R/W         | 1          | W          |             | ←Read / Write     |

|          |          | 0                                                                             | 0                                            | 0               | 0              | 0           | 0          | 0          | 0           | ←After reset      |

|          |          |                                                                               | IN                                           | T5              |                |             | IN         | T4         |             |                   |

| INTE45   | 0071H    | I5C                                                                           | 15M2                                         | : I5M1          | : 15M0         | I4C         | 14M2       | 14M1       | : I4M0      |                   |

| 107111   | R/W      | <u>:</u>                                                                      | . W                                          |                 | R/W            | <u> </u>    | W          |            |             |                   |

|          |          | 0                                                                             | 0                                            | 0               | 0              | 0           | 0          | 0          | : 0         |                   |

|          |          |                                                                               | :                                            | T7              | -              |             | <u>IN</u>  |            | -           |                   |

| INTE67   | 0072H    | I7C                                                                           | 17M2                                         | : I7M1          | : 17M0         | I6C         | 16M2       | : I6M1     | : I6M0      |                   |

|          |          | R/W                                                                           |                                              | . W             |                | R/W         | <u>:</u>   | . W        | •           |                   |

|          |          | 0                                                                             | : 0                                          | : 0             | : 0            | 0           | : 0        | : 0        | : 0         |                   |

|          |          |                                                                               | INTT1 (1                                     |                 | : .=           |             | INTTO (1   |            | : .=        |                   |

| INTET01  | 0073H    | IT1C                                                                          | : IT1M2                                      |                 | IT1M0          | IT0C        | IT0M2      | •          | : ITOMO     |                   |

|          |          | R/W                                                                           | <u>.                                    </u> | . W             |                | R/W         | -          | <u>W</u>   |             |                   |

|          |          | 0                                                                             | 0                                            | : 0             | : 0            | 0           | <u>; 0</u> | : 0        | : 0         |                   |

|          |          | ITOC                                                                          |                                              | Fimer 3)        | : 172540       | ITOC        | INTT2 (1   |            | : 1700.00   |                   |

| INTET23  | 0074H    | IT3C                                                                          | : IT3M2                                      |                 | : IT3M0        | IT2C        | IT2M2      |            | : IT2M0     |                   |

|          |          | R/W                                                                           | <u>:</u>                                     | . w             |                | R/W         | :          | <u> W</u>  |             |                   |

|          |          | 0                                                                             | · •                                          |                 | 0              | 0           | <u> </u>   | 0          | . 0         |                   |

|          |          | ITEC                                                                          | INTTR5                                       |                 | : 175840       | IT46        | INTTR4     |            | : 174840    |                   |

| INTET45  | 0075H    | IT5C                                                                          | : 115IVI2                                    |                 | : IT5M0        | IT4C        | : IT4M2    |            | : IT4M0     |                   |

|          |          | R/W                                                                           |                                              | W<br>: 0        | : 0            | R/W         |            | W          |             |                   |

|          |          | 0                                                                             |                                              |                 | 0              | 0           | <u> </u>   | <u> </u>   | 0           |                   |

|          |          | ITTC                                                                          | INTTR7                                       |                 | : IT7M0        | ITEC        | INTTR6     |            | : IT6M0     |                   |

| INTET67  | 0076H    | IT7C<br>R/W                                                                   | : 1171012                                    |                 | : IT7M0        | IT6C<br>R/W | : IT6M2    |            | : IT6M0     |                   |

|          |          | 0                                                                             | 0                                            | <u>W</u><br>: 0 | . 0            | <b>-</b>    | 0          | W<br>: 0   | . 0         |                   |

|          |          | - 0                                                                           |                                              | •               | 0              | 0           | -          |            | <u>;</u> 0  |                   |

|          |          | ITX0C                                                                         |                                              | TX0<br>: ITX0M1 | : ITYONIO      | IRX0C       | INT        |            | : IRX0M0    |                   |

| INTES0   | 0077H    | R/W                                                                           | TIAUIVIZ                                     | W               | : ITXUIVIU     | R/W         | INAUIVIZ   | W          | ; IIIXOIVIO |                   |

|          |          | 0                                                                             | 0                                            |                 | . 0            | 0           | . 0        | 0          | . 0         |                   |

|          |          |                                                                               | INT                                          |                 | . •            | - Ŭ         | INT        |            | . •         |                   |

|          |          | ITX1C                                                                         |                                              | ITX1M1          | ITX1M0         | IRX1C       |            |            | : IRX1M0    |                   |

| INTES1   | 0078H    | R/W                                                                           |                                              | W               | : 117(11410    | R/W         | HOTHVILE   | W          | HOTHER      |                   |

|          |          | 0                                                                             | 0                                            | . 0             | . 0            | 0           | 0          | : 0        | . 0         |                   |

|          |          | ·                                                                             | INT                                          | •               |                |             | INT        |            |             |                   |

|          |          | ITC1C                                                                         | : ITC1M2                                     |                 | ITC1M0         | ITC0C       | : ITC0M2   |            | : ITC0M0    |                   |

| INTETC01 | 0079H    | R/W                                                                           | :                                            | w               |                | R/W         | :          | W          |             |                   |

|          |          | 0                                                                             | 0                                            | 0               | 0              | 0           | 0          | 0          | : 0         |                   |

|          |          |                                                                               | INT                                          | TC3             |                |             | INT        | TC2        |             |                   |

| ====     |          | ITC3C                                                                         | ITC3M2                                       |                 | : ITC3M0       | ITC2C       | ITC2M2     |            | : ITC2M0    |                   |

| INTETC23 | 007AH    | R/W                                                                           |                                              | W               | -              | R/W         |            |            |             |                   |

|          |          | 0                                                                             | 0                                            | 0               | 0              | 0           | 0          | 0          | 0           |                   |

|          |          | <b>—</b>                                                                      | L                                            |                 |                |             |            |            |             | •                 |

| lxxM2    | lxxM1    | lxxM                                                                          | 0                                            | •               | Function       | (Write)     |            | <b>=</b> i |             |                   |

| 0        | 0        | 0                                                                             | Pro                                          |                 | rrupt requ     | iest.       |            |            |             |                   |

| 0        | 0        | 1                                                                             |                                              |                 | request le     |             |            |            |             |                   |

| 0<br>0   | 1 1      | 0                                                                             |                                              |                 | request le     |             |            |            |             |                   |

| 1        | Ö        | 1 Sets interrupt request level to "3". 0 Sets interrupt request level to "4". |                                              |                 |                |             |            |            |             |                   |

| 1        | 0        | 1                                                                             | 1 Sets interrupt request level to "5".       |                 |                |             |            |            |             |                   |

| 1<br>1   | 1 1      | 0                                                                             |                                              |                 | t request le   |             | <b>"</b> . |            |             |                   |

| lxxC     | <u>'</u> | Function                                                                      |                                              | יייטייט וווופ   | irapiredi<br>I |             | n (Write)  |            | ¬           |                   |

| 0        | Indica   |                                                                               | errupt req                                   | uest            | Clea           |             | pt request | flag       | $\dashv$    |                   |

| 1        |          |                                                                               |                                              |                 |                |             | t care     |            | -           |                   |

|          | •        |                                                                               | Indicates interrupt request.                 |                 |                |             |            |            |             |                   |

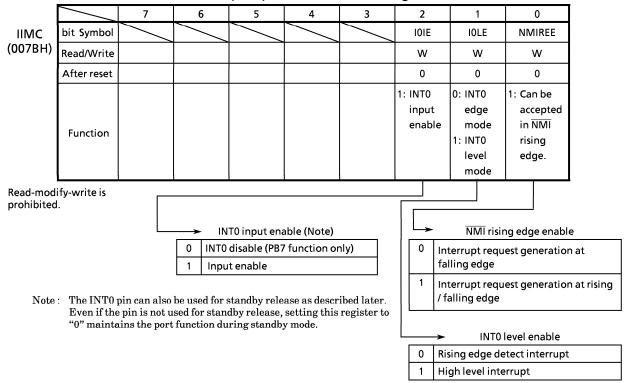

## (2) External interrupt control

## Interrupt Input Mode Control Register

## **Setting of External Interrupt Pin Functions**

| Interrupt | Pin name | Mode                     | Setting method                                    |

|-----------|----------|--------------------------|---------------------------------------------------|

|           |          | ¬∟ Falling edge          | IIMC <nmiree> = 0</nmiree>                        |

| NMI       | _        | Falling and rising edges | IIMC <nmiree> = 1</nmiree>                        |

| INITO     | 202      | _f Rising edge           |                                                   |

| INT0      | PB7      | Level                    |                                                   |

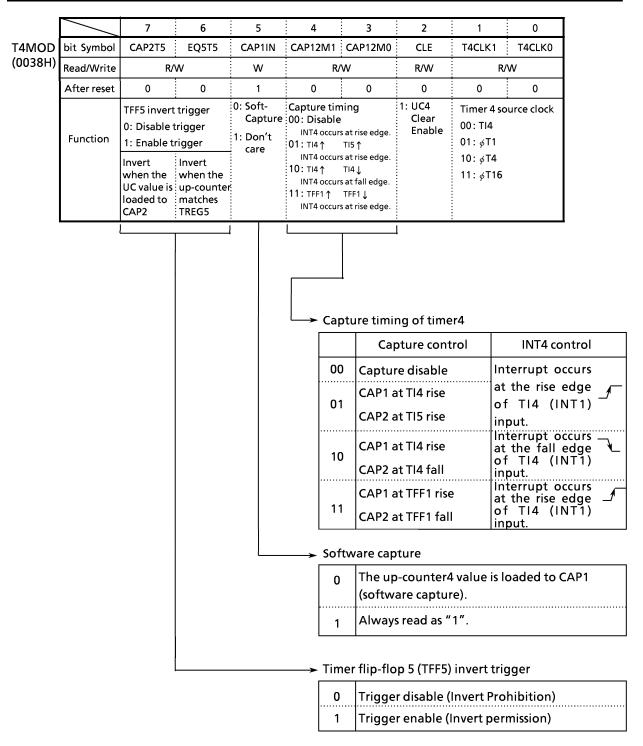

| 15.17.4   | 220      | _ <b>√</b> Rising edge   | T4MOC <cap12m1,0> = 0,0 or 0,1 or 1,1</cap12m1,0> |

| INT4      | PB0      | Falling edge             | T4MOD <cap12m1, 0=""> = 1, 0</cap12m1,>           |

| INT5      | PB1      | _√ Rising edge           |                                                   |

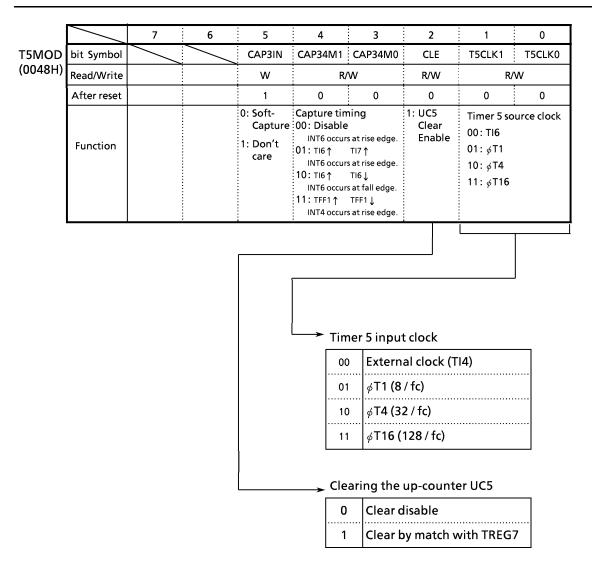

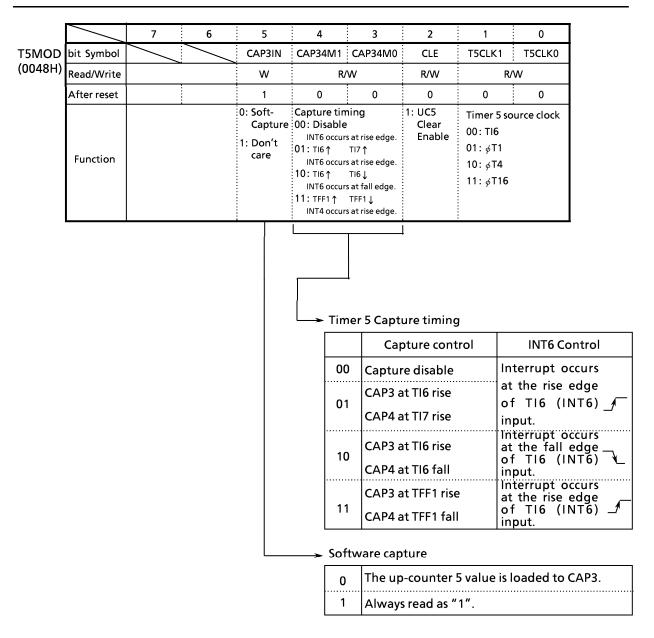

| INITC     | DD 4     | _ <b>√</b> Rising edge   | T5MOC <cap34m1,0> = 0,0 or 0,1 or 1,1</cap34m1,0> |

| INT6      | PB4      | Falling edge             | T5MOD <cap34m1, 0=""> = 1, 0</cap34m1,>           |

| INT7      | PB5      | Rising edge              |                                                   |

#### (3) Micro DMA start vector

Register used to assign micro DMA processing to an interrupt source. The interrupt source whose micro DMA start vector matches the vector value set in this register is assigned as the micro DMA start source.

When the micro DMA transfer counter value reaches 0, the interrupt controller is notified of the micro DMA transfer end interrupt corresponding to the channel, the micro DMA start vector register is cleared, and the micro DMA start source of the channel is also cleared. To continue the micro DMA processing, the micro DMA start vector register must be set again within the micro DMA transfer end interrupt processing.

If the same vector is set in the micro DMA start vector registers of the multiple channels, the interrupt generated in the channel with the smaller number has a higher priority.

Thus, if the same vector is set in the micro DMA start vector registers of two channels, the interrupt generated in the channel with the smaller number is processed until the micro DMA transfer end. If the micro DMA start vector of this channel is not set again, the next micro DMA is started for the channel with the higher number. (micro DMA chaining)

|                  | N           | /licro DN | /IA0 Star | t Vector |                                      | (re    | ad-modify-v | write is not p  | oossible.) |

|------------------|-------------|-----------|-----------|----------|--------------------------------------|--------|-------------|-----------------|------------|

|                  |             | 7         | 6         | 5        | 4                                    | 3      | 2           | 1               | 0          |

| DMA0V            | bit Symbol  |           |           |          | DMA0V8                               | DMA0V7 | DMA0V6      | DMA0V5          | DMA0V4     |

| DMA1V<br>(007DH) | Read/Write  |           |           |          |                                      |        | W           |                 |            |

|                  | After reset |           |           |          | 0                                    | 0      | 0           | 0               | 0          |

|                  | N           | licro DM  | IA1 Start | Vector   |                                      | (re    | ad-modify-  | با write is not | oossible.) |

|                  |             | 7         | 6         | 5        | 4                                    | 3      | 2           | 1               | 0          |

|                  | bit Symbol  |           |           |          | DMA1V8                               | DMA1V7 | DMA1V6      | DMA1V5          | DMA1V4     |

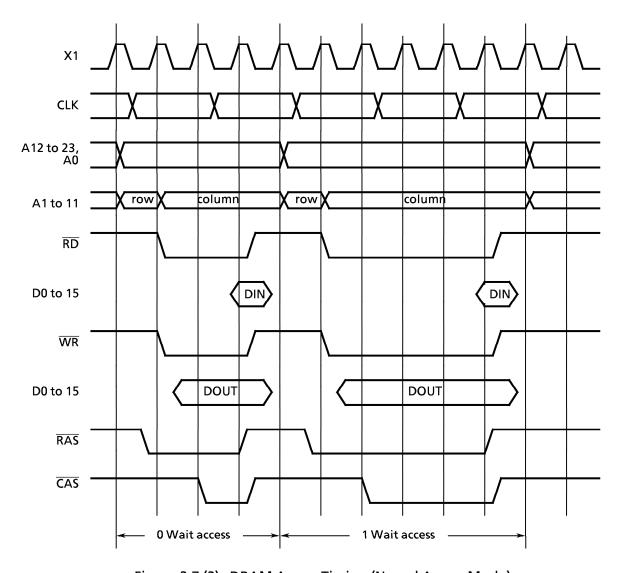

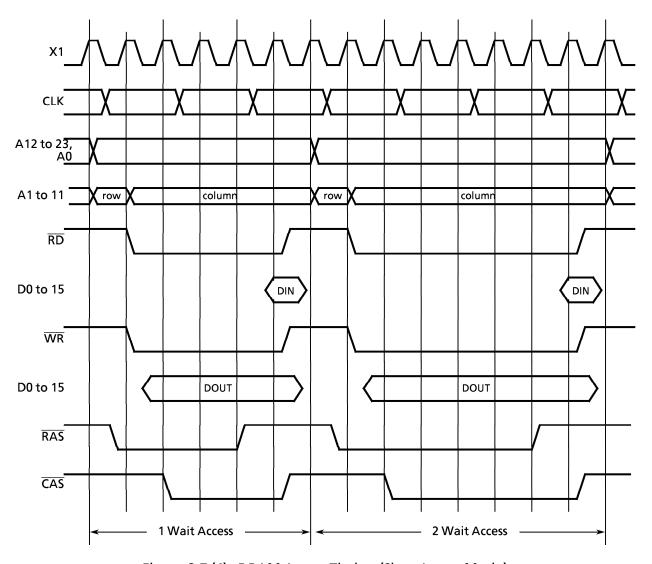

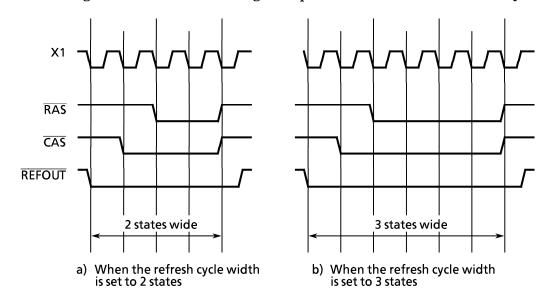

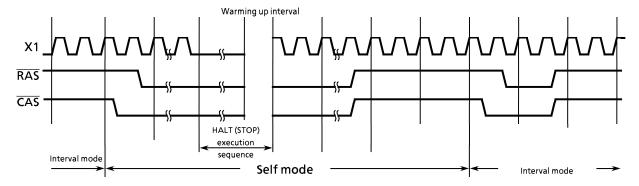

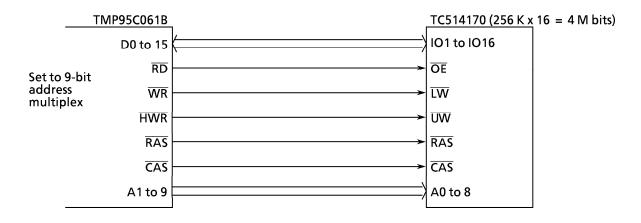

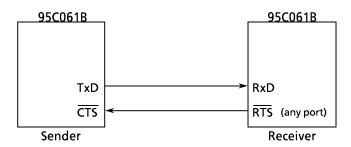

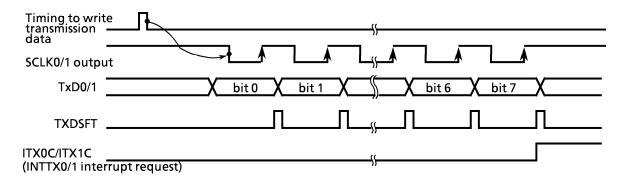

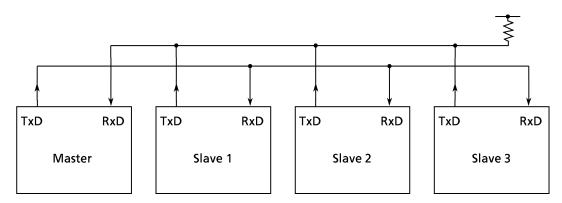

| (007DH)          | Read/Write  |           |           |          |                                      |        | W           |                 |            |